이번에는 Control Unit 의 구조와 구현 방법에 대해서 살펴보겠습니다.

Topics

- Micro-Operations

- control of Processor

- Hardwired Implementation

Micro- Operations 에 대해 배워보겠습니다.

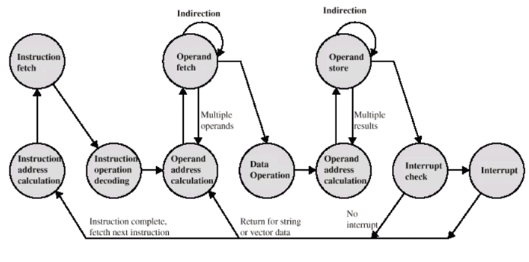

이전에 이런 자료를 보았습니다. 페치/실행 cycle 입니다. 얼핏보면 한 사이클이라고 생각하겠지만 이건 한 사이클이 아닙니다. 수많은 여러 사이클로 구성이 되어있습니다.

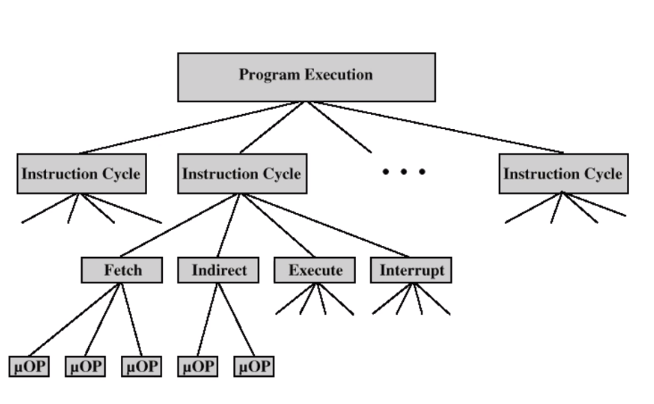

그러니 Micro-Operations은 이렇게 각 cycle 을 더 세부적인 단계로 나눈겁니다.

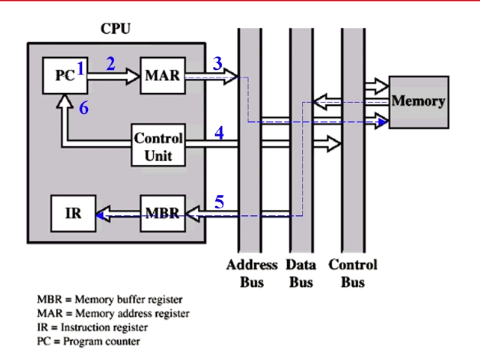

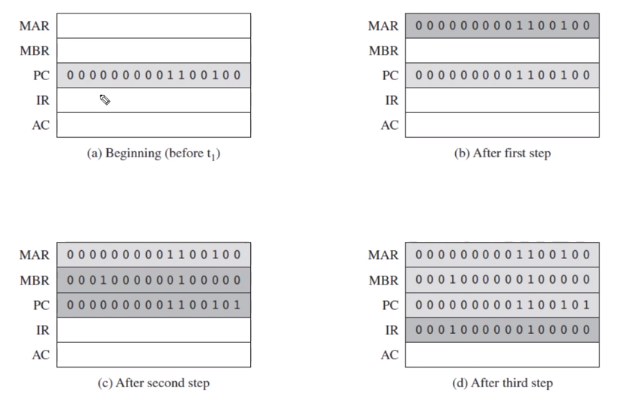

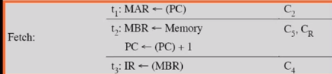

이제 이 Fetch 단계에 대해서 자세하게 보도록 하겠습니다. 이것도 예전에 배웠던 겁니다 .

명령어 페치는 메모리로 부터 명령어를 가져와서 실행시키는 거죠.

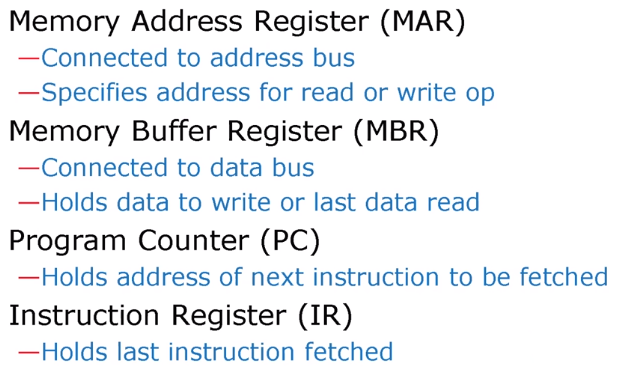

페치에는 다음과 같이 이미 배웠던 네개의 레지스터가 필요합니다.

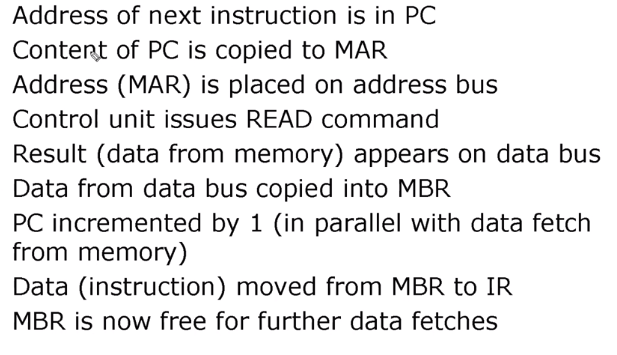

아래는 페치 순서입니다.

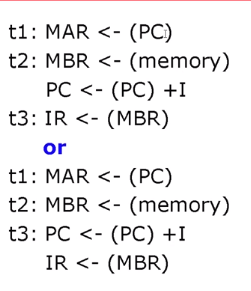

Symbolic 하게 보겠습니다.

Rules for Clock Cycle Grouping

방금 본 t2, t3 처럼 어떻게 Grouping 을 할거냐라는 내용입니다.

- Proper sequence must be followed : 적절한 순서를 지켜야합니다. 당연하게도

- Conflicts must be avoid

- Also PC <- (PC) + I .involvew addition

이런 경우는 하지 말라는 의미입니다.

Indirect Cycle

IR address 를 따라간다고 바로 operand 가 나오지 않고 그게 있는 주소가 또 있었습니다. 그니깐 두번의 direct 인거죠.

t3 에서 주소 정보를 address 쪽으로 가서 이걸 활용해서 무엇갈 하겠다는 의미 입니다.

Interrupt Cycle

인터럽트 처리를 위해 다른 정보를 저장합니다. stack에

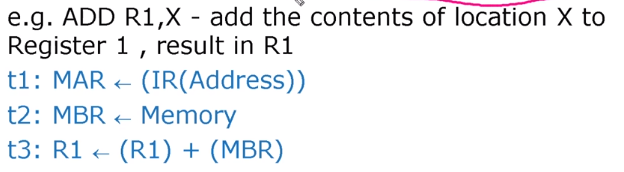

Execute Cycle(ADD)

명령어들에 따라 다른 길이의 마이크로 오퍼레이션을 가집니다.

MAR 주소 에 해당되는 값이 MBR 로 간다는 의미 입니다.

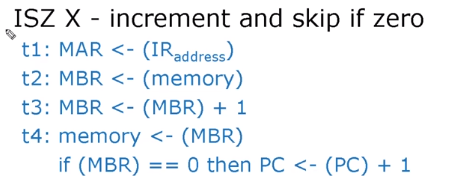

Execute Cycle(ISZ)

X 가 제로가 되면 스킵을 합니다.

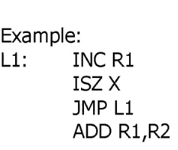

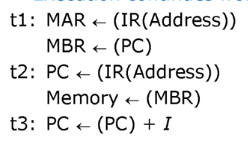

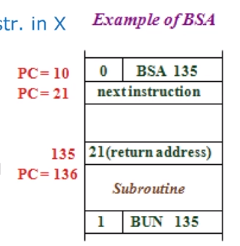

Execute Cycle(BSA)

BSA X - Branch and save address

BSA 의 다음 명령어 주소가 X에 저장이 된다는 의미입니다.

즉 BSA 135 를 하면 이 다음 명령지 136이 subroutine 이라는 의미입니다. 이걸 끝내면 다시 21 번으로 다음 명령이 실행이 됩니다.

Instruction cycle

그래서 이때까지 받던거 처럼 인터럽트나 페치나 더 작은 명령어 스텝으로 실행이 가능하다는 걸 알 수 있습니다.

Control of Processor

프로세서의 제어를 확인해보겠습니다.

하드웨어적인 여러 구성 요소들을 적절히 동작하게 하는게 프로세스 컨트롤입니다.

이를 위해서 두가지가 충족되어야합니다.

1. Sequencing : 순서를 잘 유지

2. Exectution

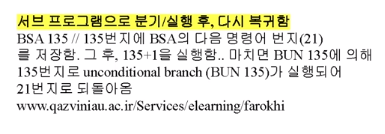

결국 Control Unit 이라는 게 뭐냐면 아까 말한거처럼 컨트롤을 잘 할 수 있게 하는 겁니다.

그니깐 내가 해야하고자 하는 명령어과(Instruction register) 현재 상태 (Flags)에 따라서

적절하게 내부와(control signals within CPU) 외부의(Control signals to control bus) 컨트롤 시그널을 잘 만들어 내는 겁니다.

물론 이때 외부의 신호도(Control signals from control bus) 잘 활용합니다.

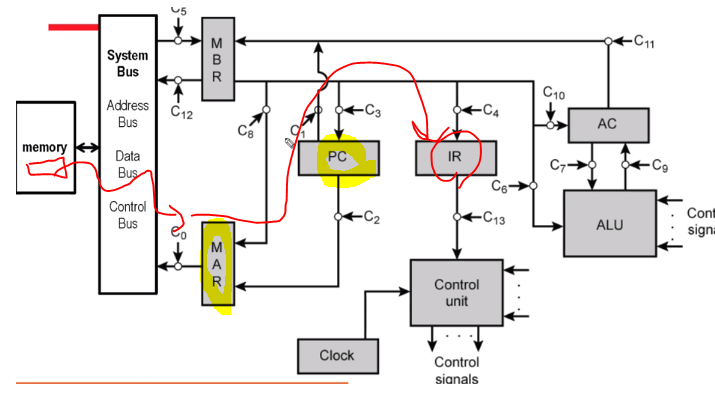

아래 그림으로 설명을 해보겠습니다.

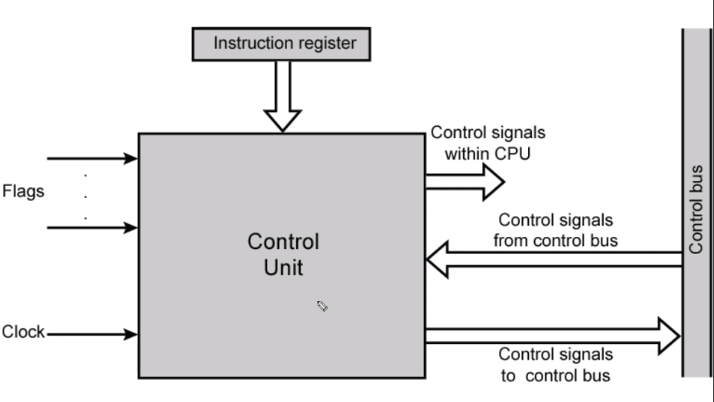

여기서 CPU 내부는 어딜까요?

이 부분입니다.

fetch 는 어떻게 하나요?

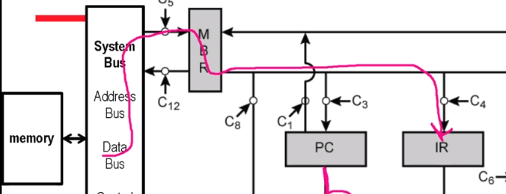

다음 처럼 PC에 있는 Address 가 MAR를 통해서 버스를 통해서 특정 주소의 있는 명령어를 데이터버스를 통해서 잘 가지고 오는게 IR 까지 오는 게 목적이었습니다.

그럼 어떤 부분들을 컨트롤 해야하니냐

PC와 MAR 사이의 C2를 On 시켜야합니다. (Control Signal 줘야함 이 부분에)

또 MAR 와 버스 사이도 연결을 시켜야 알 겁니다.

그러면 메모리에서 꺼낸 명령어는 버스를 통해 IR 로 이렇게 갑니다. (위 그림을 틀렸습니다.)

이 부분를 잘 공부해야합니다!

'공부 > 컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터구조17 Parallel Processing (0) | 2020.07.03 |

|---|---|

| 컴퓨터구조14 Instruction Level Parallelism and Superscalar Processors (0) | 2020.07.03 |

| 컴퓨터구조13 Reduced Instruction Set Computers (0) | 2020.07.03 |

| 컴퓨터구조12 CPU Structure and Function (0) | 2020.06.30 |

| 컴퓨터구조11 Instruction Sets : Addressing Modes and Formats (0) | 2020.06.30 |