지난 시간에 비동기식 카운터까지 보았습니다.

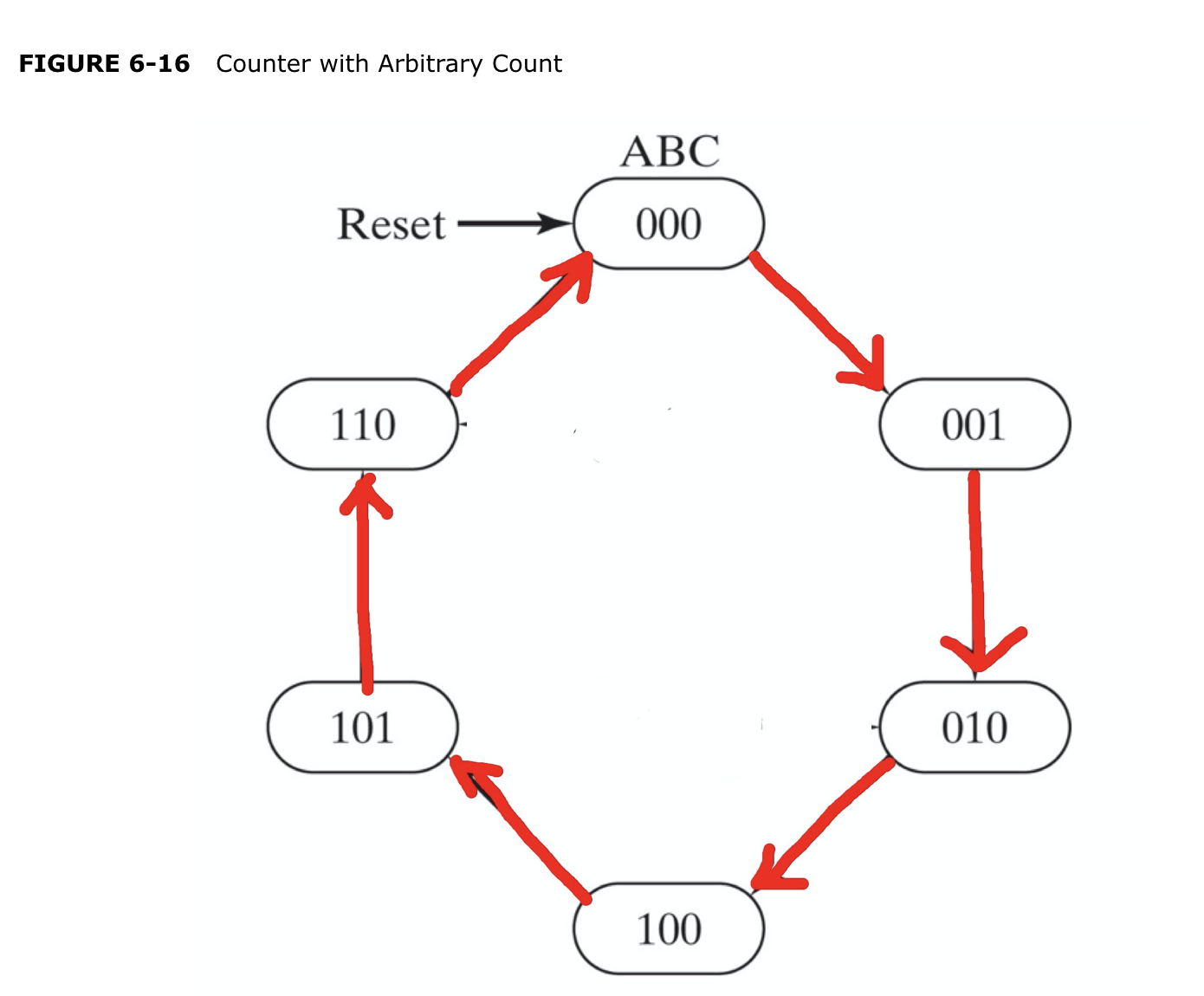

일반적 카운터를 봅시다.

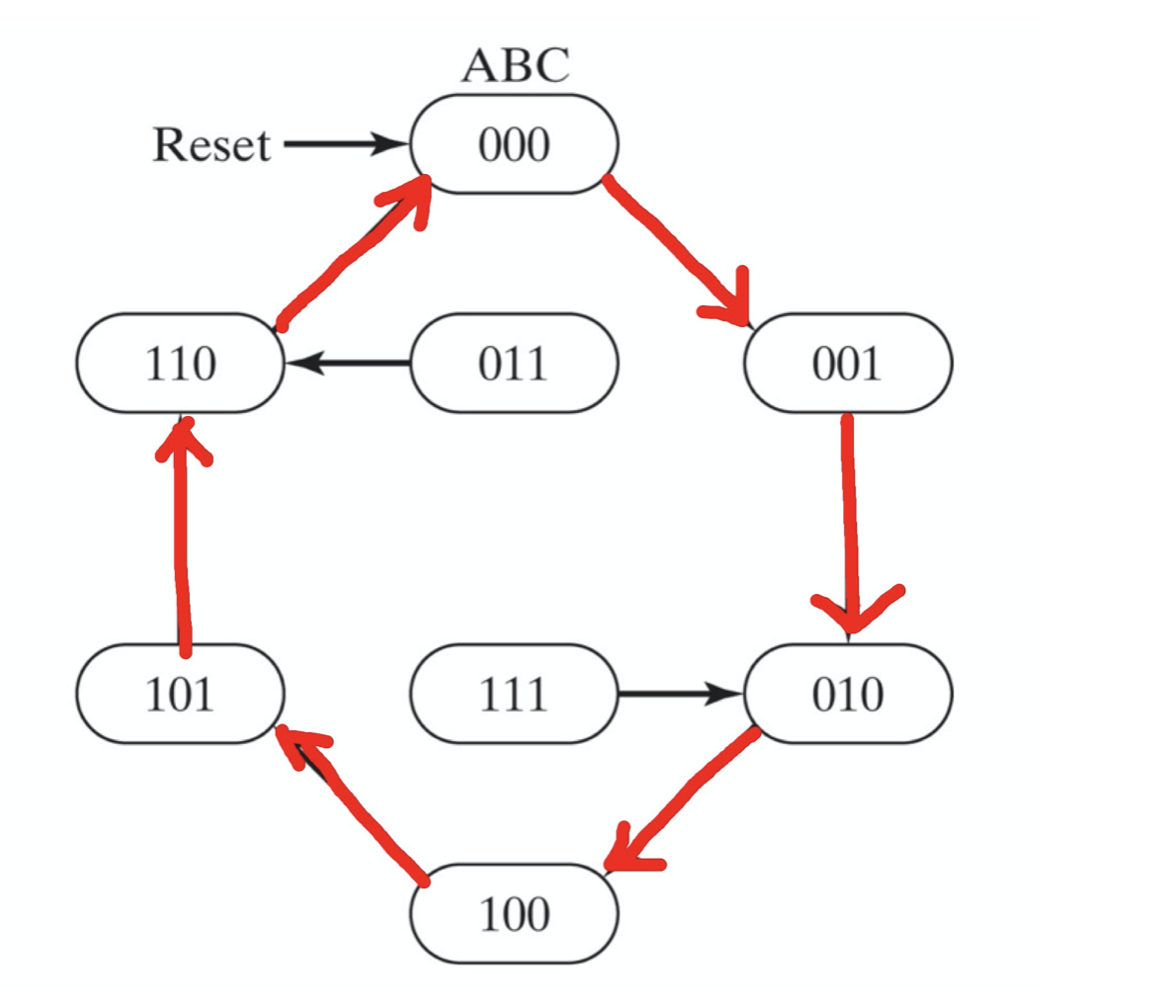

이런식으로 카운팅을 하는 카운터를 설계하고 싶다면 4장에서 배운 동기식순차회로의 게이트 수준 설계 방법을 그대로 사용하면 됩니다. 단 4장에서의 상태천이표와 다른 점은 4장에서의 상태천이표에서는 상태가 심볼들이어서 이 심볼들 을 이진코드로 바꾸는 상태할당이 필요하였는데 이 카운터를 위한 상태천이도는 이미 상태들이 카운터의 이진 코드들로 표기되어 있음으로 상태할당이 필요 없습니다.

그것 빼고는 나머지 과정들은 4장에서의 과정을 그대로 따라가면 됩니다.

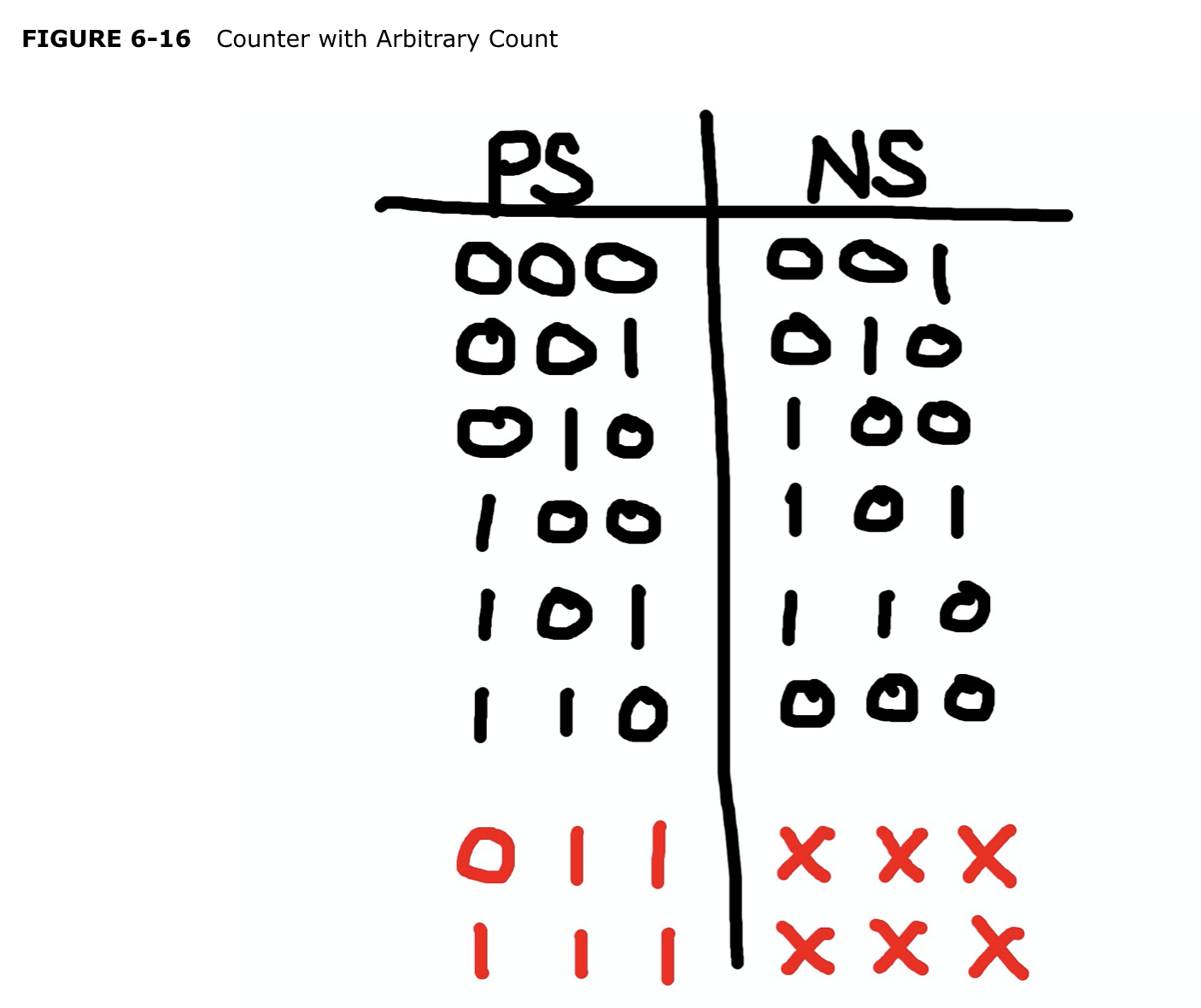

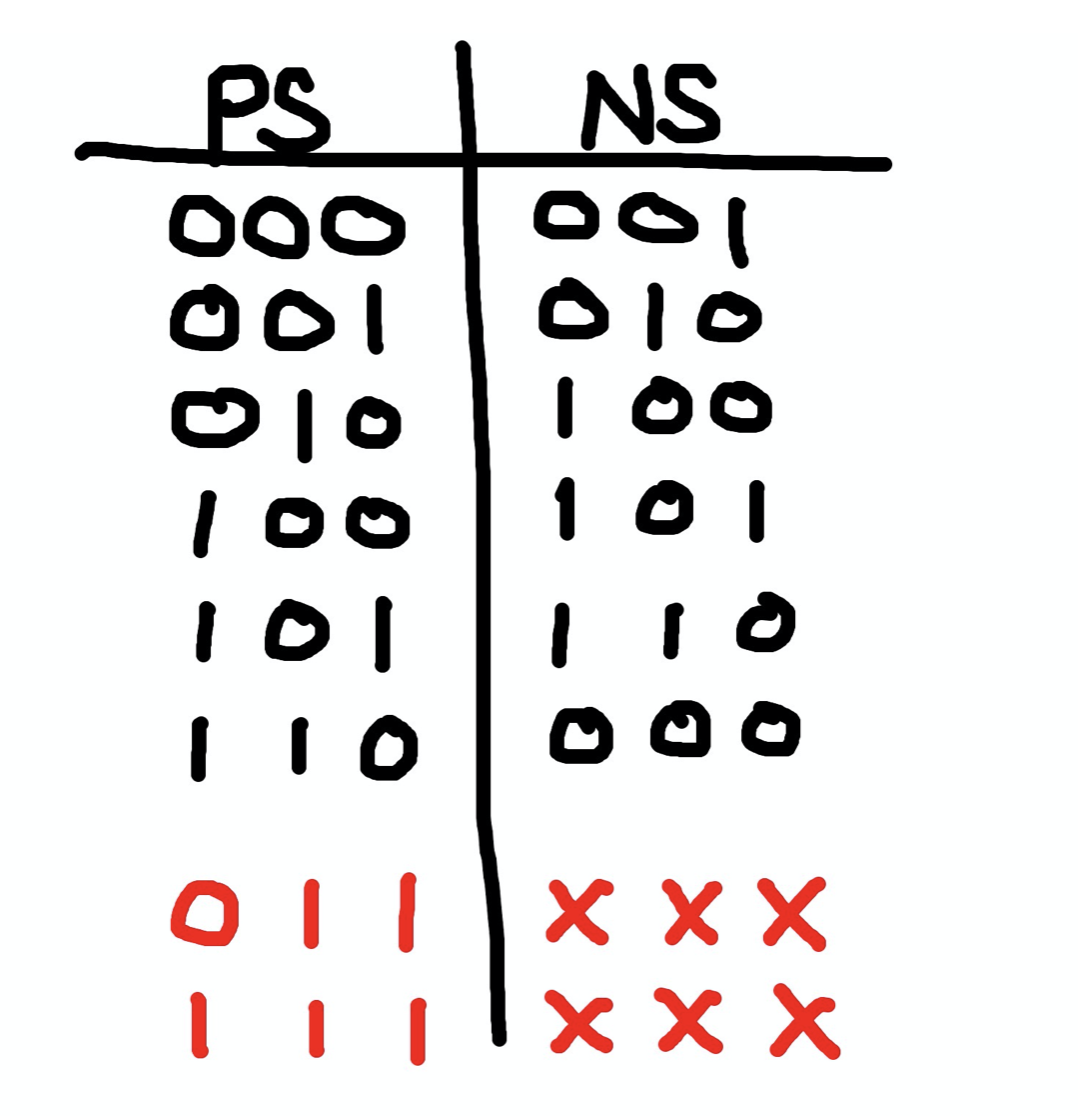

그래서 이것으로부터 만들어지는 조합회로부에 대한 진리표는 다음과 같습니다.

여기서 아래 부분이 조합회로의 입력입니다.

그리고 아래가 조합회로의 출력입니다.

여기서 아래 빨간색 이진코드는 원래의 상태천이도에 존재하는 카운팅 시퀸스인데 위 그림에 없음으로 현재 상태가 다음 이진 코드와 같은 경우에는

다음과 같이 Don't care 로 처리될 수 있습니다.

2장에서 배운대로 이 6자리의 Don't care는 0이나 1이나 아무거나 될 수 있다는 의미입니다.

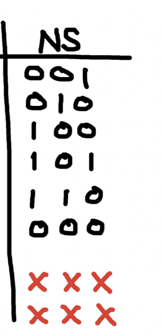

그래서 만일 최적화 입장에서

이렇게 되어야한다면 그 상황에서는 다음과 같이 회로가 구현이 되는겁니다.

그래서 내가 원래 원하는 카운팅 시퀸스(빨간경로)로 동작하는 경우에는 상관이 없지만 만일 오동작으로 현재 상태가 011로 가버리면

이 시퀸스에서 빠져나올 수가 없습니다. 빠져나오는 유일한 방법은 RESET=1 시키는 방법만이 유일합니다.

근데

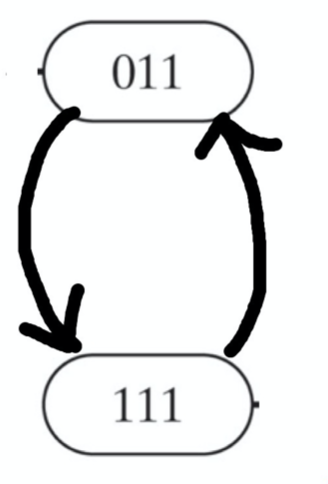

여기에서 Don't Care에 대해서 고려해서 최적화는 덜 되더라도 다음과 같이 구현을 하였다면

오동작으로 현재 카운터값이 011이 나 111이 되더라도 그 다음 클럭에서 다시 원래의 카운터시퀸스로 자동적으로 복귀할 수 있습니다. 그 다음 클럭에서 다시 원래의 즉, 최적화를 덜하더라도 오동작 상황에서도 신뢰성 높은 회로로 설계하고 싶은 경우에는 이렇게 하는 것이 필요하다는 예입니다.

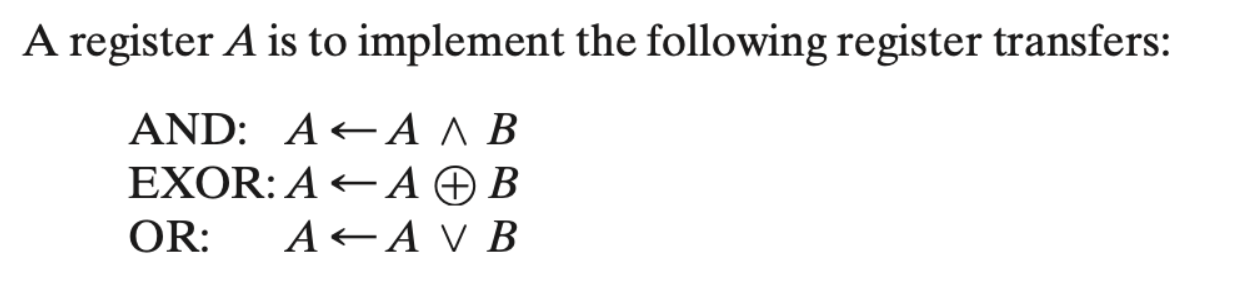

레지스터 설계 예를 보기로 합시다.

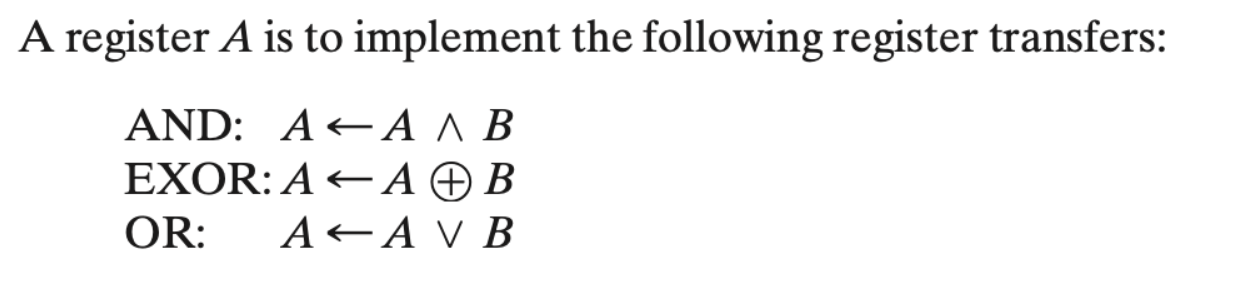

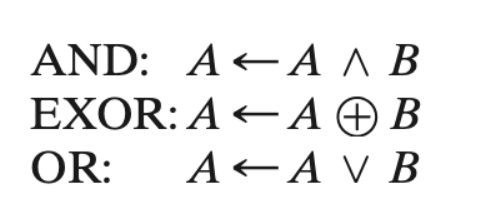

다음과 같이 3가지 동작을 할 수있는 레지스터 A를 설계하고 싶습니다. 조건은 다음과 같아요.

즉

1. AND,EXOR,OR가 2개 이상 동시에 1이 될 수 없다

2. AND,EXOR,OR 가 모두 0인 경우에는 당연히 a를 가지고 있는 값을 유지한다.

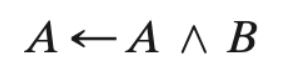

그래서 AND = 1 이면 다음 트랜스퍼가

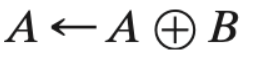

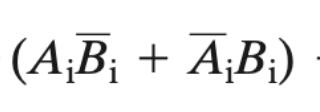

EXOR = 1이면 다음 트랜스퍼

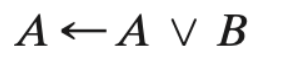

OR=1 이면 다음 트랜스퍼

가 일어나도록 레지스터 A를 설계하라

책에서는 게이트 수준 설계로 그냥 들어갔지만 이는 잘못된 방법 입니다.

논리 설계는 항상 레지스터 전송 수준에서 설계를 다 한 후 게이트 수준 설계를 해야합니다.

레지스터들은 죄다 데이터 패스에 있습니다. 그럼 AND,EXOR,OR 시그널은 누가 만들어 지는가?

Control Unit 이 만들어 줍니다.

그 시점, 해당 시그널이 1이 될때에 해당 액션이 일어나게 되는 것

따라서 Control Unit 이 해당 레지스터트래스퍼가 일어나는 시점을 결정하는 것.

(중요)

그럼 레지스터 전송 수준 설계를 해봅시다.

레지스터전송수준설계가 게이트 수준 설계보다 훨씬 쉽습니다.

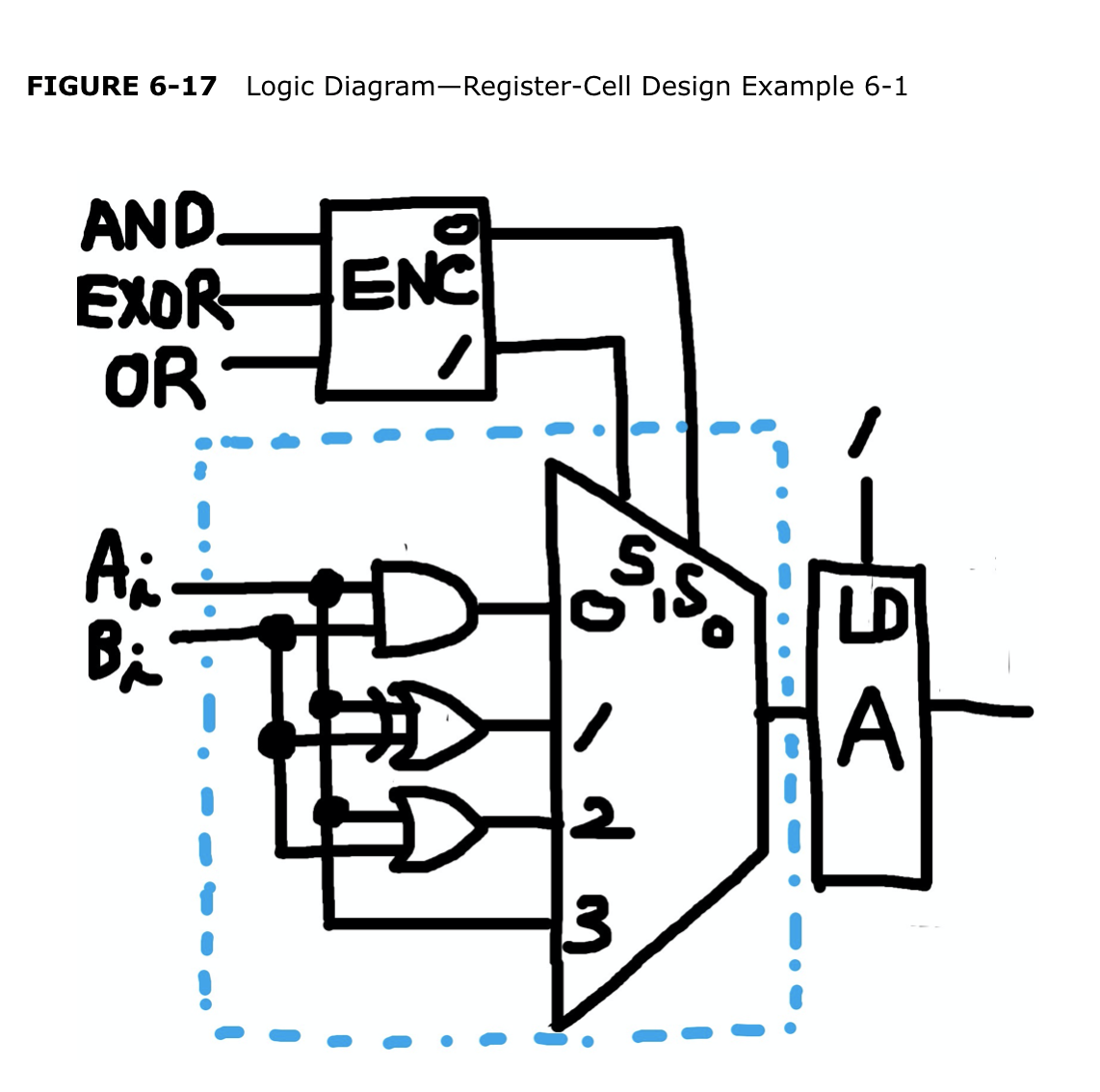

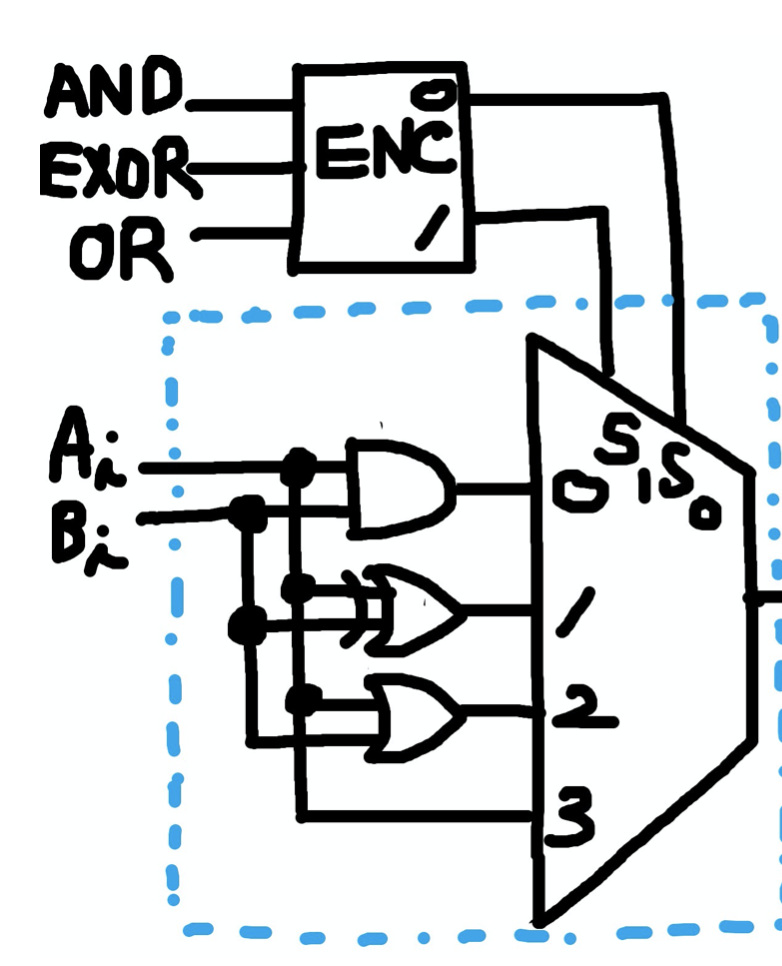

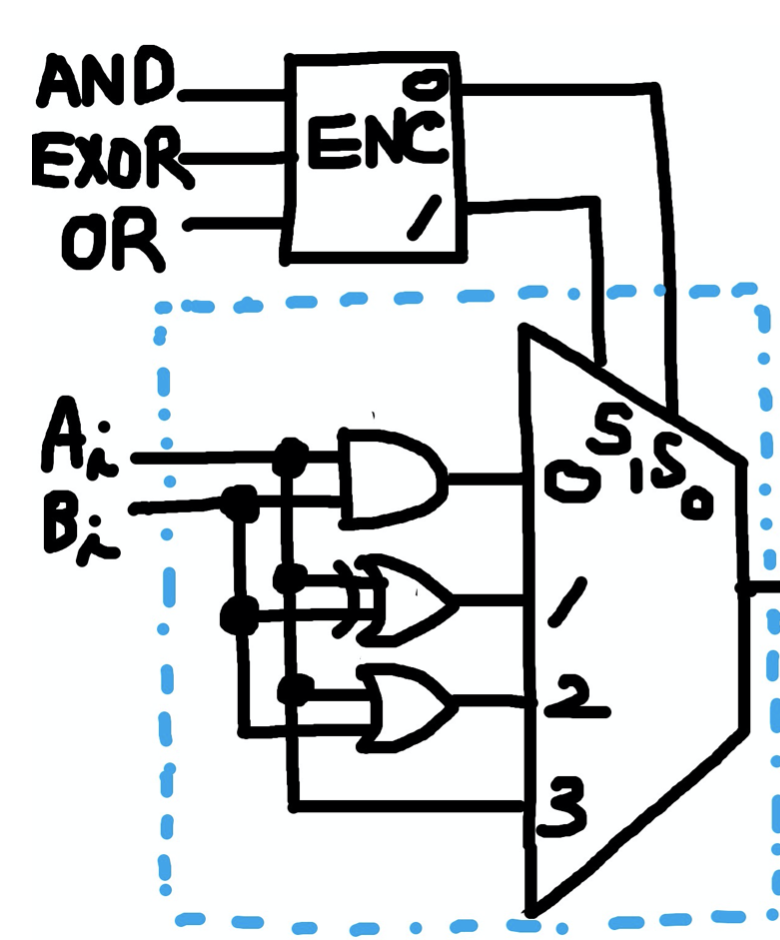

아래가 레지스터 전송 수준 설계입니다.

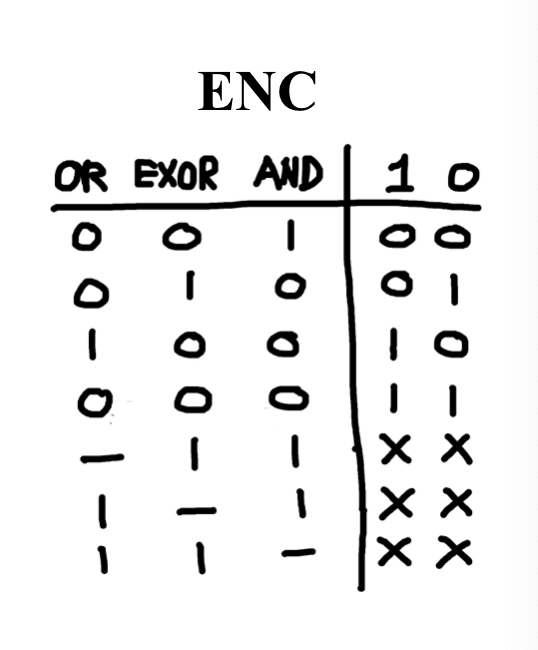

조합회로 ENC의 진리표는 다음과 같습니다.

여기서도 레지스터 전송수준 설계는

이것으로 부터 나옵니다.

문제를 보고 이런 구조를 생각해 내야합니다. 이것을 할 수 있어야 레지스터 전송 수준 설계를 할 수 있는 겁니다.

여기서 진리표의 -(하이픈) 은 돈케어가 아닙니다. 이것은 0과 1을 모두 포함한다는 내용입니다.

-11 은 011 과 111 이겠죠.

이건 어디서 나오는 걸까요?

컨트롤 유닛입니다

이와 같은 스키메틱과 진리표를 얻으면 레지스터 전송 수준 설계를 완료한 것입니다. 이 다음엔 게이트 수준 설계를 하면 되는 거죠.

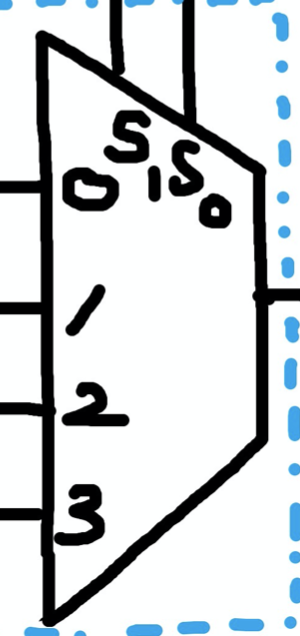

즉 게이트 수준 설계는 레지스터 전송 수준 설계에 사용된 로직블럭(컴포넌트)들에 대해서 설계를 하면 되는데, 여기 예에서 사용된 컴포넌트들은 4개입니다.

그런데 앞의 3 조합회로 블럭들이 합쳐지면 최적화를 할 수 있는 상황들이 많이 발생됩니다.

그래서 이것들을 산업체에서는 사람이 하지 않고 소프트웨어가 자동적으로 수행하게 되는데 우리는 여기서 사람이 메뉴얼하게 하는 방식을 좀 봅시다. 즉

이 조합회로부에 대한 최적화된 게이트 수준 스키메틱을 얻는 방법입니다.

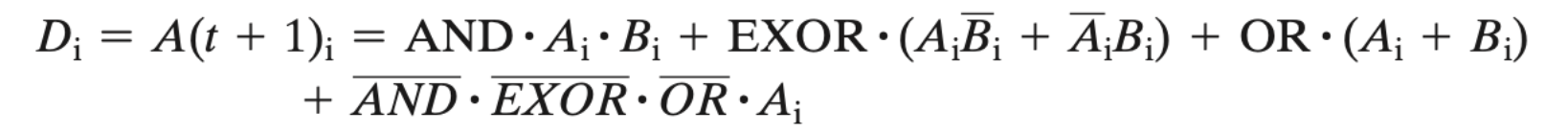

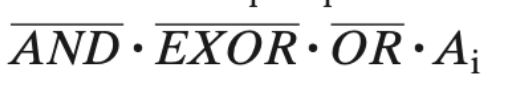

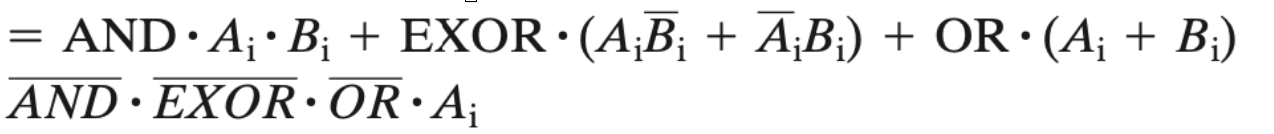

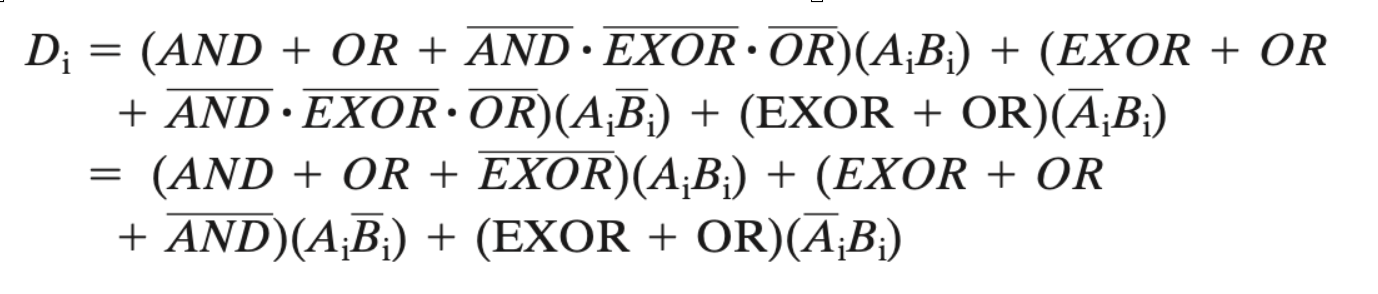

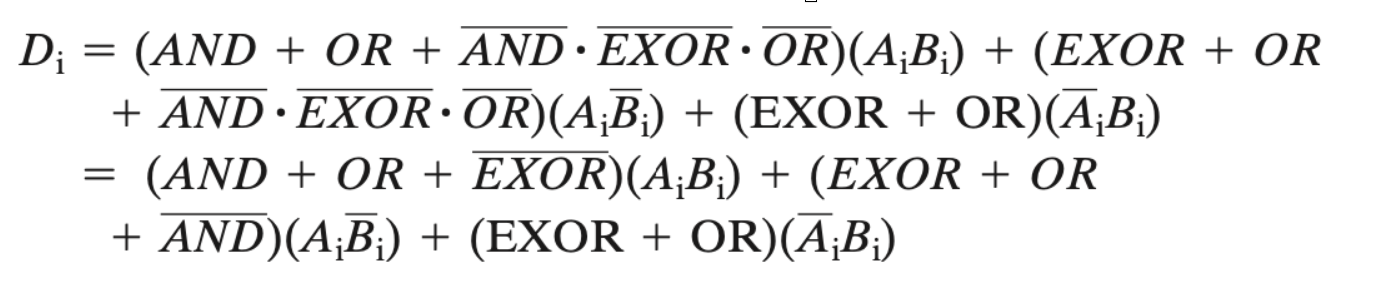

이 Di 식은 레지스터 A의 한비트 한비트를 구성하는 D 플립플롭의 입력 D에 대한 부울식을 표현한 것입니다.

즉 AND = 1 일때는 (EXOR = OR = 0)

이 식에서

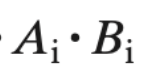

의

만 남음으로 비트별 AND 를 하게 되고, EXOR = 1일 때는 (AND=OR=0임),

이 식에서

만 남아서 비트별 EXOR를 하게 되고

OR = 1일때는 (AND = EXOR = 0)

이 식에서

만 남아서 비트별 OR 를 하게되고

OR = AND = EXOR = 0 일 때는

의

만 남아서 비트별로 현재 값을 받아들임으로

이 동작을 하는 식

이 식을 다시 정리해서 쓰면

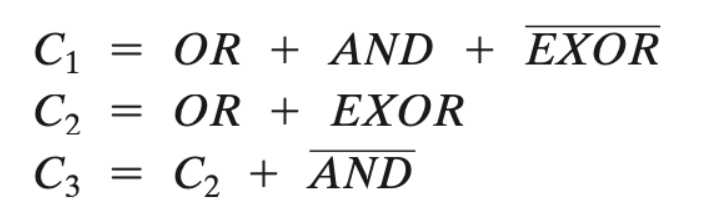

이 식 여기서

요렇게 중간 변수를 사용하면

이 식이

다음과 같이 됩니다.

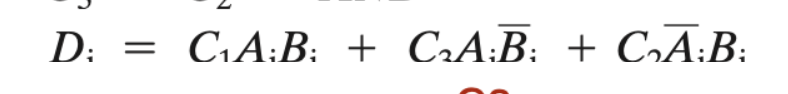

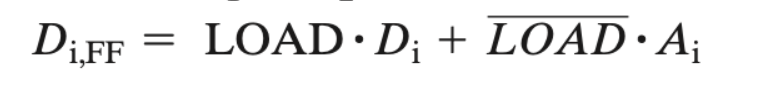

최종 Di FF는 이것입니다.

그래서 이것에 대한 스키메틱을 그린 것이 나중에 나오는데 우선

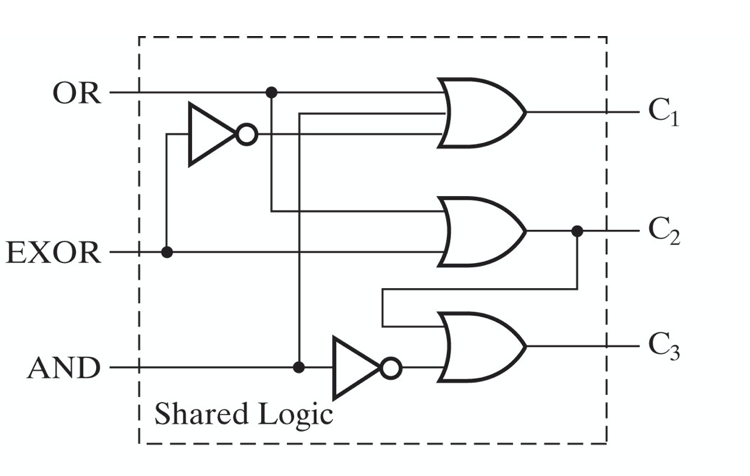

Control Unit으로부터 오는 OR,EXOR,AND로 C1,C2,C3 를 생성하는 로직입니다.

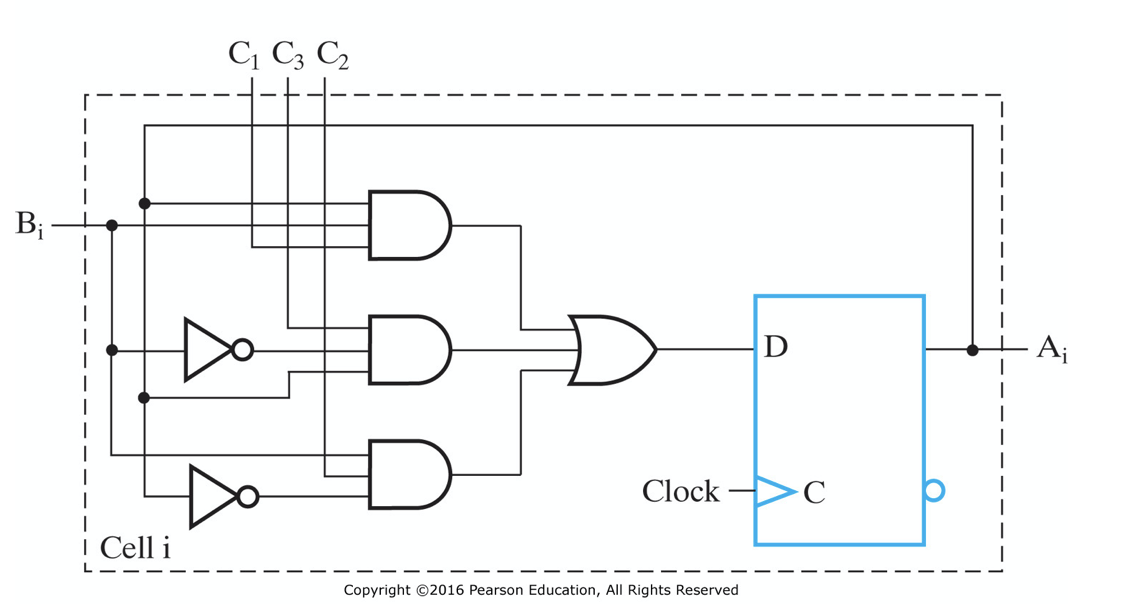

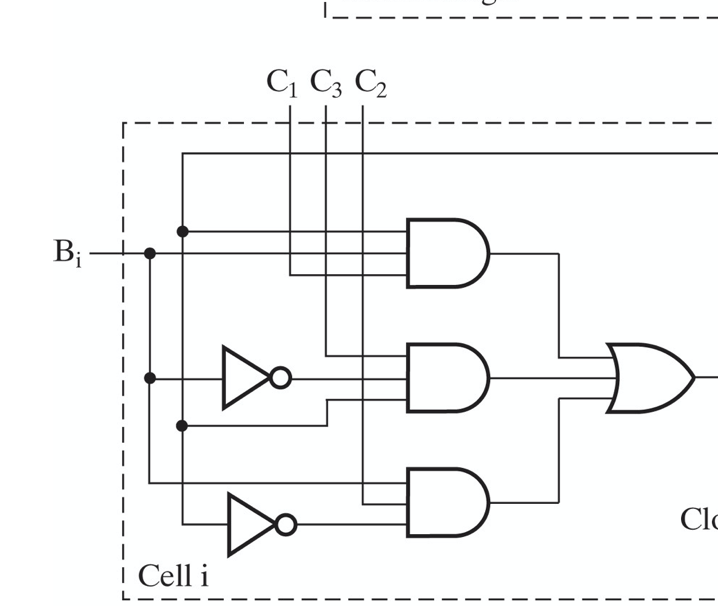

그리고 레지스터 A의 각 비트별로는 이렇게 하면 됩니다.

각 비트별로 최적화가 된 부분을 보여주고 있습니다.

즉 레지스터전송수준에서는

이러한데 이것이 게이트 수준에서 최적화과정까지 거치게 되면

이렇게 바뀌게 됩니다. 하지만 요새 이건 소프트웨어가 다 합니다.

'공부 > 논리회로설계' 카테고리의 다른 글

| 논리회로설계 레지스터들 간의 연결 (0) | 2020.06.25 |

|---|---|

| 논리회로설계(레지스터 설계 예시, 비동기식 카운터 설계) (2) | 2020.06.22 |

| 논리회로설계(데이터패스,컨트롤 유닛) (0) | 2020.06.16 |

| 논리회로설계(레지스터 전송 수준에서의 논리설계방법) (0) | 2020.06.12 |

| 논리회로설계(레지스터전송수준설계) (0) | 2020.06.10 |