우선 레지스터전송수준 설계를 하고, 그 다음에는 각 서브 블럭별로 게이트 수준 설계를 해야합니다.

소프트웨어에서 변수를 많이 사용하는 것처럼 하드웨어에서도 레지스터들을 많이 사용합니다.

마찬가지로 하드웨어에서도 많은 레지스터를 사용합니다.

예로 스마트폰 안 마이크로프로세서(AP)는 레지스터를 수천개 이상 가지고 있습니다.

이런 수천개 레지스터 사이에 레지스터 트랜스퍼가 일어날려면 하드웨어에서 물리적으로 연결이 되어야 합니다.

처음 받던 거 처럼

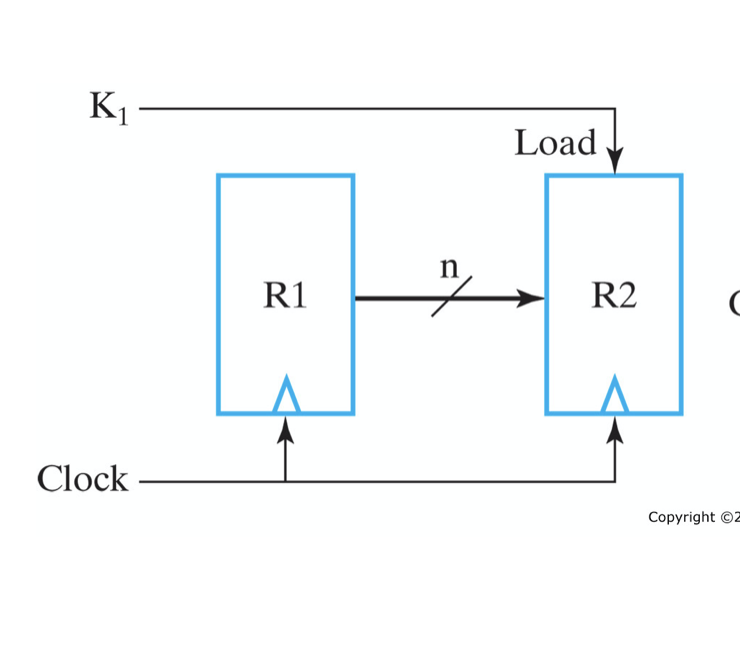

R2 <- R1 을 하려면 다음과 같이 R1의 출력에서 R2 의 입력까지 연결이 되어 있어야 합니다.

하지만 위처럼 R2가 될 수 있는게 수천 개의 레지스터 중에 하나고 R1 될 수 있는 게 수천 개의 레지스터들 중에 하나라면 이들 간의 연결이 극도로 복잡해 질 겁니다.

마치 우리나라에 대도시가 1000개가 있는데 이 대도시들 간에 사람들이 수시로 왕래를 하여야 하는 경우에 비슷합니다. 이런 경우 당연히 1000개의 도시들 간에 고속도로를 다 별도로 둘 수 없습니다.

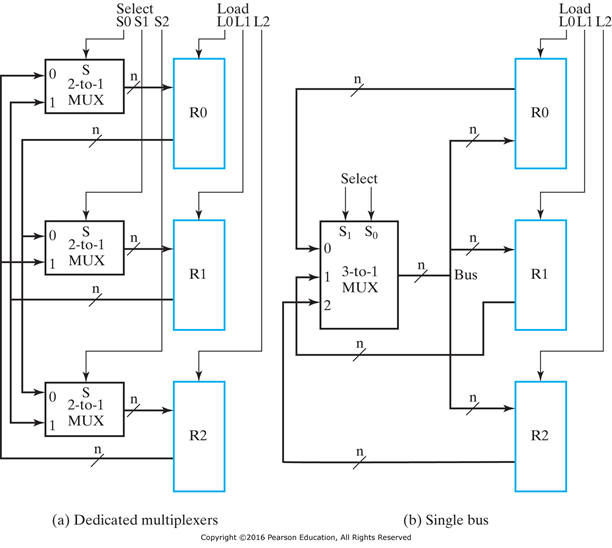

여기서도 마찬가지로 문제를 단순화 시켜서 레지스터가 3개인 다음 경우를 봅시다.

이 3개의 레지스터 간에는 레지스터 전송이 자유롭게 일어나야 하는 경우입니다.

그림 a 는 각 레지스터의 입력단마다 별도의 MUX를 두어서 별도의 경로를 따로따로 만들어준 겁니다.

이는 마치 1000개의 도시들 마다 따로따로 고속도로를 만든 것과 동일합니다.

레지스터 수가 적다면 문제가 없지만 레지스터 수가 조금만 증가하더라도 엄청난 비용이 들어가는 문제됩니다.

그에 비해 그림 b는 레지스터 별도의 MUX를 둔 게 아니라 모든 레지스터들에 대해서 1개의 MUX만을 둔 것 입니다.

우선 각 레지스터의 출력단을 MUX의 데이터 입력에 하나하나에 연결시킵니다.

그리고 MUX의 출력을 "공통적으로" 레지스터들의 입력에 동일하게 연결시킵니다.

각 레지스터들은 각각 별도의 LOAD 제어신호 Li를 가지고 있습니다.

당연히 이들 L0,L1,L2 는 Control Unit 에서 오는 신호들입니다.

이렇게 b 같이 하면 장점은 레지스터의 수가 크게 늘어나더라도 래지스터트랜스퍼를 위한 구조를 만드는 비용이 기하급수적으로 증가하지 않습니다.

a는 비용이 기하급수적으로 증가되는 방식

b는 비용이 기하급수적으로 증가되지 않는 방식

마치 우리나라에 경부, 중부, ... 고속도로가 있는 겁니다.

부산에서 서울 갈때도 울산서 서울갈때도 경부 고속도로 이용하는 것과 같은 것 -> 버스 라고 합니다.

버스는 하드웨어에서 매우 중요한 겁니다.

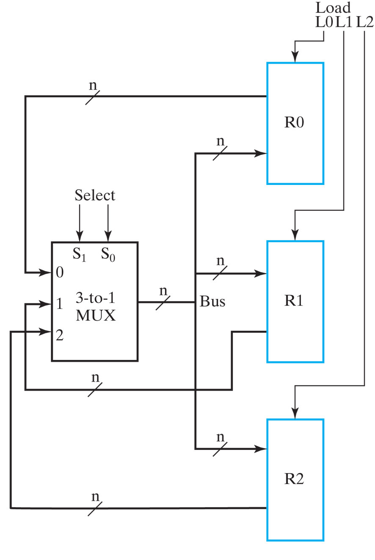

b에서 만일 R2 <- R0 을 하는 경우를 생각해보겠습니다.

그럼 S1,S0,L0,L1,L2 는 무슨 값이 되어야 할까요?

일단 S1 = S0 = 0 이어야 MUX에서 0번째 데이터, 즉 R0의 출력이 선택이 됩니다.

즉 S1 = S0 = 0 이어야하고 MUX의 출력이 모든 레지스터의 입력으로 나갈 것인데 R2가 이것을 받아들어야 함으로 , 즉 LOAD 하여야 함으로 (S0,S1,L0,L1,L2) = (0,0,0,0,1)이 되어야

R2 < - R0

이 일어납니다. 이게 레지스터 트랜스퍼를 일어나게 하는 값들인데 이 값들은 어디에서 만들어져 와야할까요?

당연히 '컨트롤 유닛 CU'입니다.

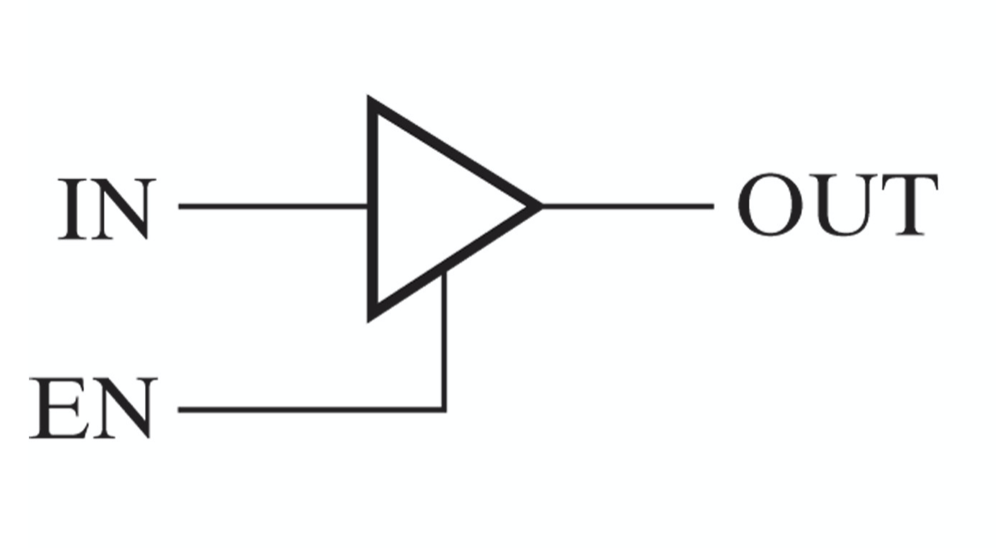

이렇게 버스는 MUX를 사용해서 구현할 수 있지만 또 다른 방법은 새로운 게이트(tri-state buffer)를 사용해서도 구현할 수 있습니다. 우선 새로운 게이트(tri-state buffer)를 봅시다.

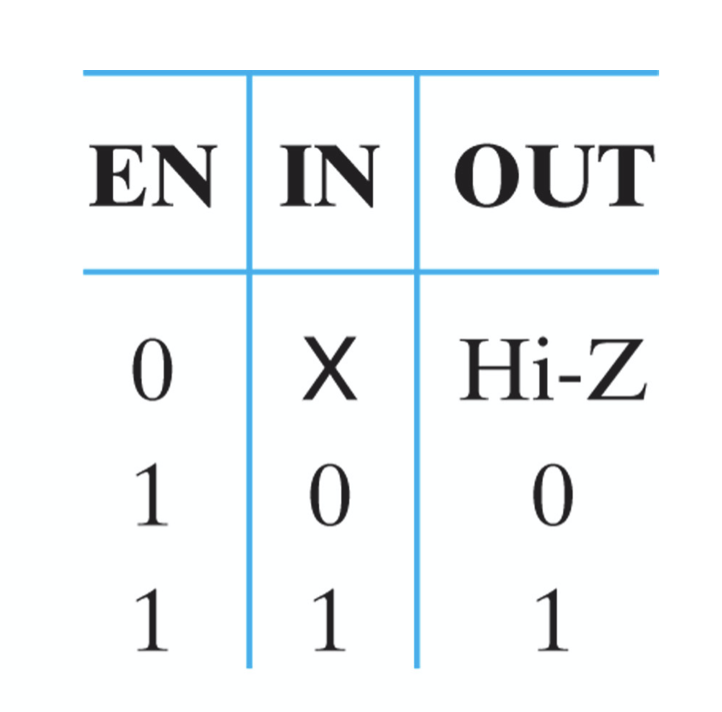

위 그림은 게이트 심볼이고 진리표는 다음과 같습니다.

출력에는 이 때까지 본 적이 없는 표현인 Hi-Z가 나오는데 이는 출력이 아무것에도 연결이 되지 않은 것을 말하는 용어입니다.

과거 교수님이 말하시길

'출력에 논리값 0 이라는 것을 회로에서 있는 제일 낮은 전압 값(통상 Ground)에 연결된 것을 말하는 것이고 논리값 1이라는 것은 회로에서 있는 제일 높은 전압(통상 인가전압 Vdd)에 연결된 것을 말하는 것이라고 했습니다.

근데 Hi-Z라는 것은 출력에 이와 같이 연결이 되지 않고 끊어진 상태라는 겁니다.

여기서는 입력 EN = 0이면 이와 같이 출력이 Hi-Z가 됩니다.

그리고 EN = 1 이면 출력은 IN과 같습니다.

즉 전기적으로 보면

EN = 1 이면 OUT 이 IN과 연결

EN = 0 이면 OUT 이 아무것에도 연결되어 있지 않다라고 생각하면 됩니다.

이와 같은 tri-state buffer 를 레지스터와 함께 아래와 같이 사용한다면

이 전체를 다음과 같은 하나의 레지스터로 볼 수 있습니다.

이 레지스터가 지금까지 본 레지스터와 다른 점 있습니다.

지금까지 본 레지스터는 입력과 출력이 따로따로 였습니다.

새로운 레지스터는 입력과 출력이 합쳐져 있었습니다.

이를 입출력(INOUT) 이라고 합니다. 말 그대로 입력도 되고 출력도 되는 형태입니다.

동시에는 아니고 어떤 때에선(EN=0) 입력, 다른 때(EN =1)에선 출력이 됩니다.

즉 방향이 양방향입니다. (기존 레지스터의 입력과 출력은 단 방햡입니다. ㅋ)

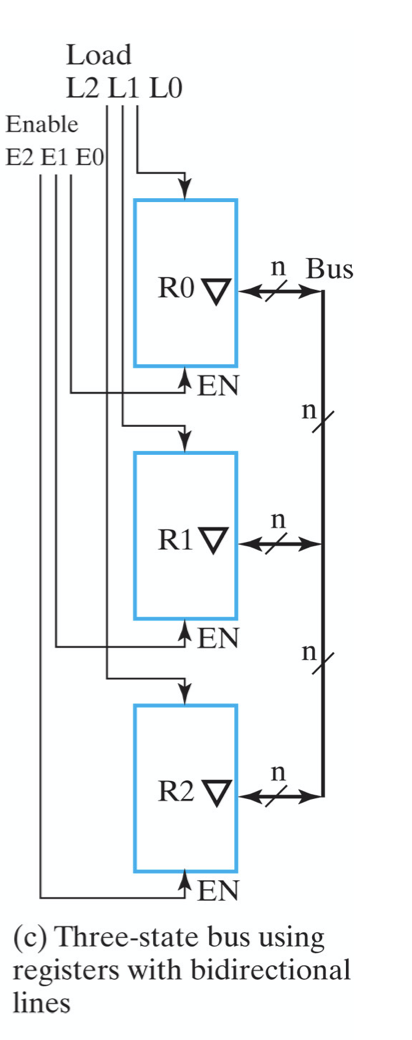

이와 같이 양방향 입출력을 가지는 레지스터를 이용하면 버스를 다음과 같이 아주 간단히 만들 수 있습니다.

이렇게 양방향 레지스터들을 이런 식으로 MUX를 사용하지 않고서 그냥 연결해주는 것으로 구성할 수 있습니다.

마지막으로 지금까지 배운 모든 것을 이용해서 하드에어 설계해보는 건 다음 포스팅으로 하겠습니다.

'공부 > 논리회로설계' 카테고리의 다른 글

| 논리회로설계 (레지스터 수준 설계 과정) (2) | 2020.06.23 |

|---|---|

| 논리회로설계(레지스터 설계 예시, 비동기식 카운터 설계) (2) | 2020.06.22 |

| 논리회로설계(데이터패스,컨트롤 유닛) (0) | 2020.06.16 |

| 논리회로설계(레지스터 전송 수준에서의 논리설계방법) (0) | 2020.06.12 |

| 논리회로설계(레지스터전송수준설계) (0) | 2020.06.10 |