안녕하세요. 옆집 컴공생입니다. 저번 주 목요일에 정리했어야 하는 내용을 이제서야 정리하네요. (양도 어마무시했습니다...) 그만큼 할 게 많아서 머리가 지끈거리는 요즘입니다. 빨리 3주뒤로 점프하고 싶은 마음이에요. 그럼! 한번 가봅시다.

아래 포스팅은 저번 주에 공부한 데이터패스와 컨트롤 유닛에 관한 겁니다.

오늘은 레지스터 설계 예시들과 비동기식 카운터설계에 대해 배워볼겁니다!

https://com24everyday.tistory.com/159

논리회로설계(데이터패스,컨트롤 유닛)

안녕하세요. 옆집 컴공생입니다. 오늘 배운 논리회로설계 복습할건데... 교수님이 진도를 아주 엄청나게 시더라구요.(필기하면서 진땀 다 뺐습니다.) 복습하는데도 한참 걸릴거 같다는 느낌이 ��

com24everyday.tistory.com

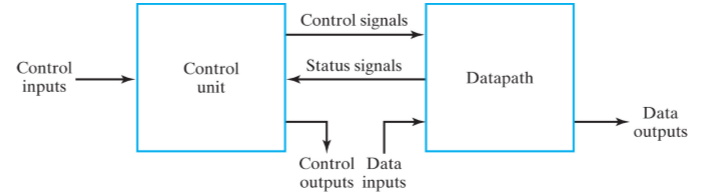

▶ CU(Control Unit) 은 상태천이표 또는 상태천이도를 만들고, 상태할당을 하고 조합회로에 대한 최적화된 부울을 구하고 스키메틱을 완성하는 것으로 설계합니다. 여기서 레지스터 전송 수준에서는 상태천이표나 상태천이도를 만드는 것까지만 하면 됩니다. 그 이후는 게이트 수준 설계입니다.

▶Datapath(데이터패스)에 대해서는 다수의 레지스터전송표기법들을 만들고 이것에서부터 데이터패스의 내부를 레지스터들과 조합회로들이 연결된 구조를 만들어 내는 것을 데이터패스에 대한 레지스터 전송 수준에서의 설계에서 하여야만 한다.

그럼 예시를 통해 한 번 알아가보도록 합시다.

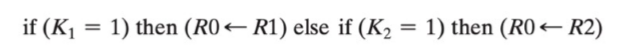

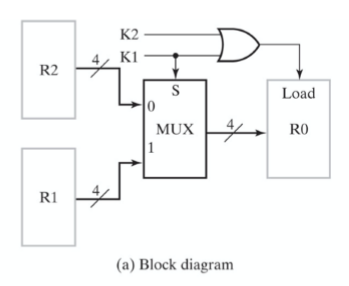

로 부터 다음을 쓸 수 있어야합니다.

저번 시간과 연결된 부분이 있습니다. 여기서 먹스가 사용된 이유는 무엇일까요? 상황에 따라서 R0에 R1을 전송하거나 또는 R2을 전송해야 하기 때문입니다.

즉 K1 = 0 이면 R0 < - R2 이고

K1 = 1 이면 R0 <- R1 입니다.

그래서 MUX 선택입력 S에 K1 을 연결합니다.

그리고 R0 레지스터에 새로운 값을 로드하는 건 K1=1 이거나 K2=1 인 경우임으로 LOAD 입력에 다음과 같이 출력 연결을 하면 됩니다.

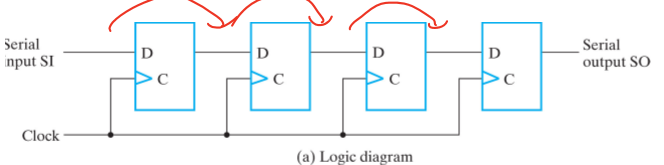

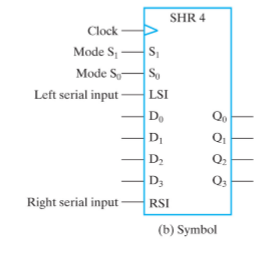

다음 그림은 4비트 쉬프트 레지스터의 예입니다.

클럭이 한번 라이징 될때마다 입력 SI 와 플립플롭들의 출력이 한 비트씩 오른쪽으로 이동합니다.

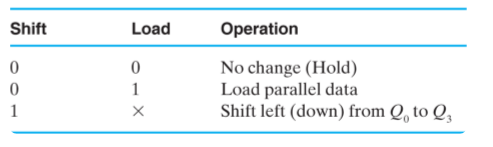

이 레지스터는 쉬프트도 되면서 병렬적 로드도 가능한 레지스터입니다.

이에 대한 동작 정의는 다음과 같습니다.

이를 부울식으로 표현하면 다음과 같습니다.

각 비트별로 존재하는 D 플립플롭 입력에 이 부울식을 구현하는 조합회로가 있어야합니다. 그게 다음과 같습니다.

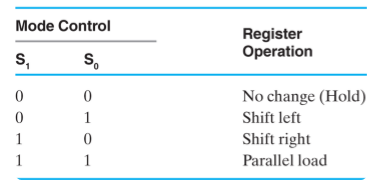

이번에는 4개의 동작을 하는 레지스터를 설계해보겠습니다.

쉬프트레프트, 쉬프트라이트, 병렬적로드, 홀드

이

이 동작은 S1과 S0입력으로 실행할 수 있습니다. (2^2 = 4)

아까 에제와 달리 이번에는 레지스터 전송 수준에서 설계 -> 설계도 빠르게 이해하기 쉽습니다.

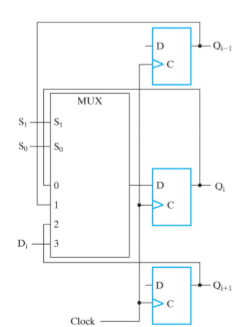

여기서 레지스터 i번째 비트만 보여주고 있는데 다른 비트들도 동일하게 생각하면 됩니다.

레지스터 각 비트 별로 4 to 1 MUX 를 두고 이 먹스는 S1,S0을 연결합니다.

그리고 먹스의 데이터 입력에 Qi, Qi-1,Qi+1,Di를 연결합니다.

그리고 먹스의 출력을 레지스터를 구성하는 해당 D 플립플롭의 입력 Di에 연결합니다.

그리고 이런 다기능동작가능레지스터(먹스 + D 플립플롭들로 된 레지스터)

이 전체를 그냥 하나의 블럭으로 하여서 "병렬로드와 쉬프트라이트/레프트 모두가 가능한 레지스터"로 다음과 쓸 수 있습니다.

이렇게 하나의 심볼로 만들어서 레지스터 전송수준설계에서 사용하게 됩니다.

내부를 보는 것은 레지스터전송수준의 설계가 끝나고 게이트수준설계를 할 때 보면 됩니다.

지금 데이터패스에 대하여 레지스터전송수준설계하는 법을 배우고 있는데 이는 매우매우 중요합니다.

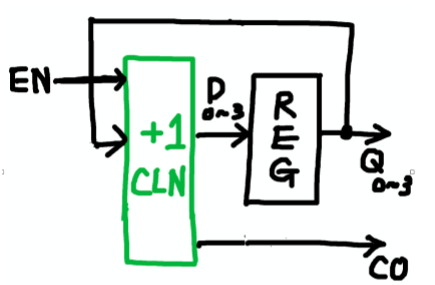

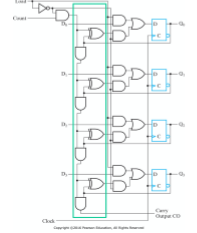

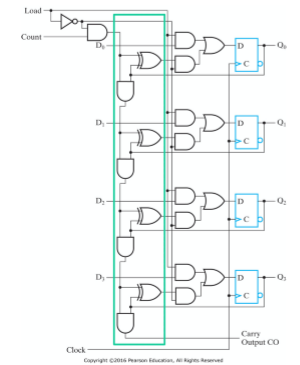

이번에는 데이터패스에서 아주 많이 사용하는 카운터 레지스터 설계에 대하여 봅시다.

카운터 레지스터

간단히 카운터는 현재 값을 증가 또는 감소 하는 동작을 합니다.

당연히 순차회로임으로 감소나 증가는 클럭이 라이징/폴링되는 순간에 일어납니다.

다음과 같은 형태일 겁니다.

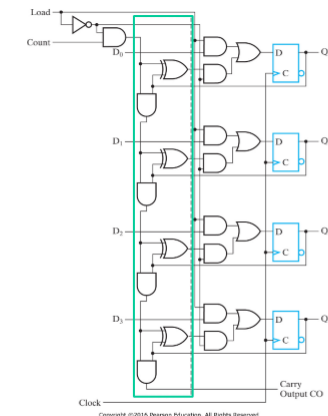

이 심볼의 내부는 다음과 같습니다.

3장에서 본 +1 하는 조합회로 EN = 1이면 즉 입력값에 +1을 해서 출력으로 나가는 조합회로입니다.

따라서 이 조합회로의 입력이 레지스터의 출력에 연결되어 있음으로 이의 출력인 D0~D3 에는 현 레지스터의 Q보단 +1이된 값이 나오게 됩니다. 단 EN=1일때만 가능합니다.

EN=0 이면 이 조합회로의 출력은 입력과 동일합니다. 그래서 클럭이 라이징 될때에 이 값이 레지스터에 들어가게 됩니다.

따라서 EN=1 경우에는 매 클럭 라이징마다 Q값이 +1 증가

EN=0 이면 Q값 변화는 없음 따라서 정확히 Up Counter 동작하게됩니다.

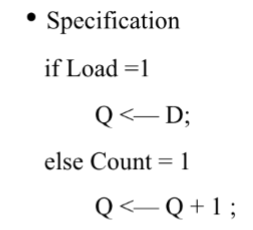

레지스터 트랜스퍼 동작은 다음과 같습니다.

우리가 먼저 설계할 건

이게 아니라

이걸 먼저 해야합니다. 그리고 아래의 과정처럼 구체화를 시켜야합니다.

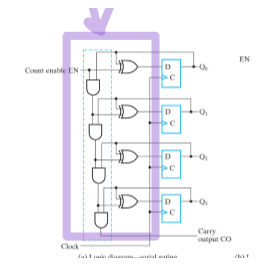

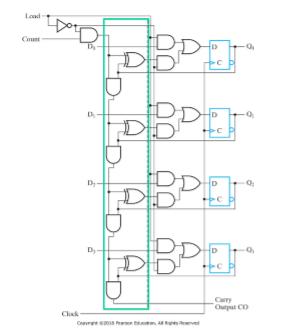

이렇게 해서 최종적으로 나오는 회로가 다음과 같습니다.

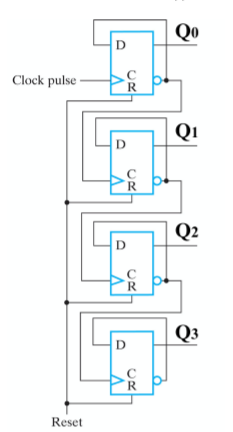

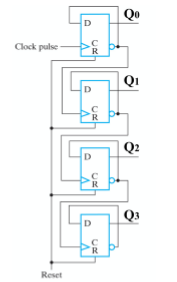

이번에는 전혀 다른 카운터의 예를 봅시다.

여기도 플립플롭이 4개가 있습니다. 지금까지 보아온 4비트 레지스터 같은데 이전 레지스터와 근본적으로 다른 점이 있습니다. 뭘까요?

바로 '클럭 입력이 다르다!' 입니다.

지금까지 본 레지스터들은 레지스터 각 비트를 구성하는 플립플롭에 모두 동일한 클럭이 들어갔습니다.

하지만

이 그림에서는 4개의 플립플롭의 클럭 입력이 다 다릅니다.

이러면 동기식이라고 할 수 없습니다. 동기식이란 클럭이 모두 동일하게 들어가는 걸 말합니다.

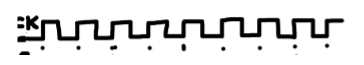

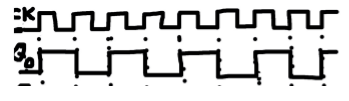

외부에서 들어가는 Clock Pulse 입력은 다음과 같습니다.

그럼 첫번째 플립플롭의 출력 Q0는

단 Reset이 제일 처음에 1이었다가 0이 되고 난 이후 상황입니다. 이것은 즉 Reset=1이면 이 Reset은 이전에 배운 것과 같이 asynchronous reset 임으로 클럭과 상관없이 Q값이 0이 됩니다.

->Reset=1로 모든 플립플롭들의 초기값을 0 으로 만들어줍니다.

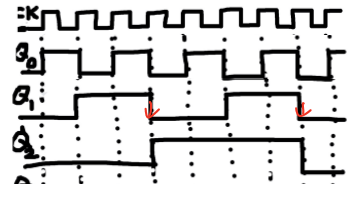

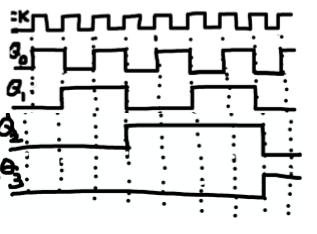

두번째 플립플롭의 클럭 입력은 첫번째 플립플롭 ^Q0에 연결되어 있음으로 Q1의 값은 아래와 같이 변화합니다.

동일하게 세번째 플립플로브이 클럭 입력은 두번째 플립플롭 ^Q1에 연결되어 있음으로 q2값은 다음과 같습니다.

마마지막 네번째 플립플롭은 다음과 같습니다.

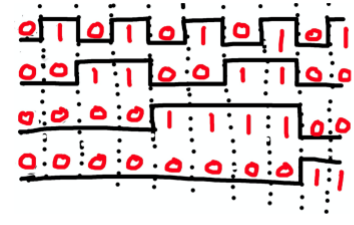

q전체를 보면 다음과 같습니다.

이런 식으로 회로도 클럭이 라이징 될때마다 q값이 +1 증가하는 카운팅을 하게 됩니다.

이전에 본 카운터와 다른 점은 이전에 다음과 같은 조합회로가 필요했지만

이건 조합회로 없이도 카운팅을 할 수 있는 것이 장점입니다.

하지만 장점만 있지는 않겠죠.

큰 단점이 존재합니다.

여기에서 Q0 Q1 Q2 Q3 에 지연시간을 고려하여 표시한 것이 빨간색 파형입니다.

여기를 기준을 상위 비트로 올라갈수록 점점 증가되는 이유를 알겠나요?

클럭 연결을 동일한 클럭을 사용하지 않고 Qi+1 클럭은 ^Qi으로 했가 때문에 출력을 통해 클럭입력을 하므로 딜레이가 누적됩니다. 즉 Q3에서 올바른 값을 얻기 위해서는 4d만큼 기다려줘야합니다. Q64면 64d만큼 기다려야겠죠.

이는 빠른 카운팅이 불가하다는 의미입니다.

위 회로는 64비트라고 하더라도 64개의 플립플롭에는 동일한 클럭이 들어감으로 지연시간 누적이라는 게 발생하지 않습니다. 즉 훨씬 빠른 카운팅이 가능합니다.

이와 같이 동일한 입력 클럭을 사용하는 카운터를 '동기식 카운터'(Synchronous Counter)' 라고 합니다.

그리고 동일하지 않는 건 Asynchronous Counter 라고 합니다.

'공부 > 논리회로설계' 카테고리의 다른 글

| 논리회로설계 레지스터들 간의 연결 (0) | 2020.06.25 |

|---|---|

| 논리회로설계 (레지스터 수준 설계 과정) (2) | 2020.06.23 |

| 논리회로설계(데이터패스,컨트롤 유닛) (0) | 2020.06.16 |

| 논리회로설계(레지스터 전송 수준에서의 논리설계방법) (0) | 2020.06.12 |

| 논리회로설계(레지스터전송수준설계) (0) | 2020.06.10 |