안녕하세요. 옆집컴공생입니다. 저번 시간에는 레지스터 전송수준설계에 대해 배웠죠. 오늘은 이에 대해 더 배워보겠습니다!

https://com24everyday.tistory.com/138

논리회로설계(레지스터전송수준설계)

안녕하세요. 옆집컴공생입니다. 오늘도 논리회로설계 수업 리뷰를 해보겠습니다.ㅎㅎ 아래 포스팅은 저번 주 강의 내용입니다. https://com24everyday.tistory.com/119 논리회로와 설계(레지스터) 오늘 배�

com24everyday.tistory.com

복습

레지스터 전송은 소프트웨어의 변수할당과 같습니다.

그럼 변수 할당은 A = B 뿐만 아니라 A = B + C 가 가능한데 이런 식이 레지스터 전송에서도 가능할까요?

정답은 '네, 할 수 있습니다' 입니다.

이를 위한 레지스터 전송 수준 설계에서 가장 먼저 해야할 것은 조합회로세어 진리표를 구하는 거 처럼 '다수의 레지스터 전송 기법을 구하는 것' 입니다.

이를 위해서는 '설계 스펙'이 있어야합니다.

▶아주 간단한 설계스팩 예시를 들어 보겠습니다.

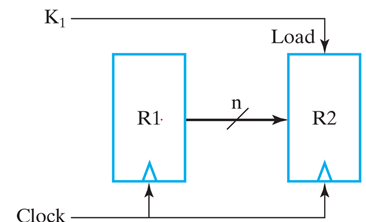

문제 : 입력 신호 K1이 일때 레지스터 R1의 내용을 레지스터 R2로 전달하는 설계를 하시요.

소프트웨어로 코드화 한다면 다음과 같겠죠.

if(k==1) R2 <- R1;

저희는 레지스터 전송 표기법을 우선 찾는 것이 설계에서 제일 먼저 해야할 것 입니다.

지난 시간에 배운 레지스터 전송 표기 방식에 근거하여 구해지는 레지스터 전송 표기법은 바로

K1 : R2 <- R1;

입니다.

그림은 다음과 같겠습니다.

그럼 R1 <- A + B 의 스키메틱은 어떻게 그려야할까요?

다음과 같이 그려야합니다.

파란 A,B,R1은 레지스터임으로 클럭과 입력이 존재합니다. 반면 녹색인 덧셈기는 조합회로기 때문에 클럭이 존재하지 않습니다. 여기서 덧셈기는 n비트 덧셈기로 일반화를 해서 생각해야합니다. (예 : ripple carry adder)

질문 : 클럭이 필요한 조합회로가 있나?

정답 : 없음

반면에 레지스터는 반드시 클럭이 필요합니다.

여기서는 클럭을 하나만 사용하고 있는데 다른 클럭을 사용해도 될까요?

물론 고급 논리 설계에서는 여러 개의 클럭을 사용하기도 합니다. 하지만 저희는 기초 논리설계이기 때문에 자칫하면 시간 개념에 대 혼란을 줄 수 있기 때문에 하나의 클럭만을 사용합니다.

클럭은 논리설계에 '시간' 개념을 도입해주기 때문에 순차회로에서 가장 중요한 입력이라고 할 수 있습니다.

너무 중요하고 당연해서 클럭 표시를 생략할 수 있습니다.

레지스터 전송 수준에서의 설계 시작점은 '다수의 레지스터 전송 표기법'을 구하는 겁니다.

다시 소프트웨어와 비교해볼까요?

소프트웨어 코딩에서는 복잡하면 복잡할 수록 변수 할당문의 갯수가 늘어납니다.

하드웨어도 마찬가지 입니다. 설계하고자 하는 논리회로의 동작이 복잡해질 수록 설계자가 생각해야하는 레지스터 전송 표기법의 개수가 증가합니다.

그럼 다수의 구체적인 예로 수십개의 레지스터 전송 표기법을 생각해야하는 경우에 함께 생각해야할 것은 무엇일까요?

두가지가 있습니다.

▶첫번째로는 '전송순서'입니다.

이해를 위해 아래 두 레지스터 전송을 볼 까요?

R2 <- R1

R2 <- A + B

'R2 <- R1' 은 단순하게 바로 전달해주면 되지만 아래의 'R2 <- A + B' 에서는 전달하는 과정에서 덧셈 연산이 먼저 수행이 되어야합니다. 즉 전송순서를 고려해야한다는 겁니다.

이처럼 레지스터 전송을 크게 나누면

첫번째와 같은 단순전달( 조합회로 안씀)과

두번째와 같은 비단순전달(대부분 조합회로 필요)로 나눌 수 있습니다.

▶두번째로는 '레지스터 전달 과정에서 어떤 가공을 하여서 전달을 할 것인가'를 생각해야합니다.

그럼 다수의 레지스터 전송들을 생각할때 이들간의 전송순서를 결정하는 과정에서 우리가 이용해야하는 것은 뭘까요?

바로 클럭이 제공하는 시간개념을 활용하여 전송순서결정을 해야합니다.

'주기적 클럭의 각 사이클 단위들이 시간 개념이 됨'

즉, 클럭의 수많은 사이클들 중에서 특정 사이클에서 해당 전송 동작이 일어나야함을 의미합니다.

첫번째 '전송순서' , 두번째 '전달과정에서의 가공'

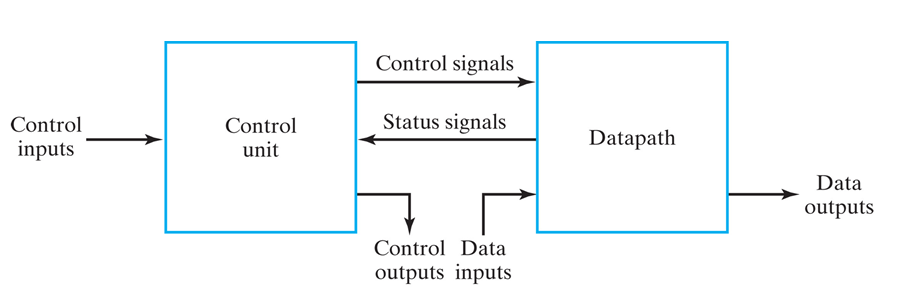

이 두가지가 올바르게 되기 위해서는 특별한 구조를 사용해야합니다. 바로 저번 포스팅 처음에 나왔던 아래 그림입니다.

이 그림에 대해서는 다음 포스팅에서 다뤄보겠습니다.ㅎㅎ

오늘은 레지스터 전송 수준에서의 논리 설계를 할 때 고려해야할 점들에 대해 배웠습니다. 수고하셨습니다.

'공부 > 논리회로설계' 카테고리의 다른 글

| 논리회로설계(레지스터 설계 예시, 비동기식 카운터 설계) (2) | 2020.06.22 |

|---|---|

| 논리회로설계(데이터패스,컨트롤 유닛) (0) | 2020.06.16 |

| 논리회로설계(레지스터전송수준설계) (0) | 2020.06.10 |

| 논리회로설계(레지스터) (2) | 2020.06.04 |

| 논리회로설계 (3) | 2020.06.02 |