안녕하세요. 옆집 컴공생입니다. 오늘은 챕터5 - Internal Memory 에 대해 알아볼려고 해요.

내부 메모리로 SRAM, DRAM, Flash Memory 의 구조에 대해 살펴보도록 할게요.

기본 요소는 Memory cell 입니다. 이는 두가지 기능을 수행할 수 있어야하는데요. 'Write와 Read' 입니다.

Ferrite Core Memory(페라이트 코어 메모리)

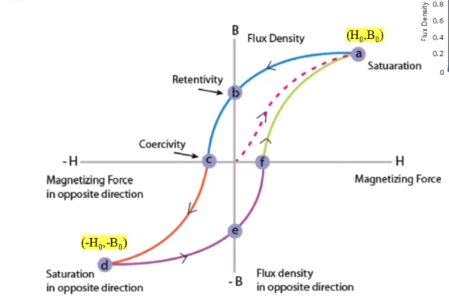

현재 반도체 메모리가 나오기 전에 사용되었던 메모리입니다. 자석이라고 생각하시면 됩니다.

또 Ferrite Core Memory 의 기본적인 동작은 Destructive read입니다. 읽으면 파괴된다는 뜻인데요. 구식이기 때문에 요새는 사용하지 않습니다.

원리를 살펴볼까요?

다음 사진에는 자화가 잘 되는 링 자석이 있습니다. 매쉬형태에 끼워져 있죠. 자화 물질(magnetic material)의 특성을 이용해 메모리를 읽고 쓰게 됩니다.

이 링은 X Drivers 와 Y Drivers 에 끼워져있습니다. 녹색 은 하나의 선이 쭉 연결되어 있습니다. 사진에서 잘 안 보이지만 하나로 다 연결되어 있는거죠.

Ferrite Core의 현재 값을 읽기 위해서는 이 링에 해당하는 X축과 Y 축에 전류를 흘려보냅니다. 그럼 이 링에 두 선에 만나는 부분이니깐 가장 많은 전류가 흘러 들어가게 됩니다. 다른 링 들은 전류가 부족하기 때문에 영향을 받지 않습니다.

현재 상태가 d 입니다. f에 있는 만큼 전류를 흘러도 뭔가 변화하지 않습니다. 다만 그보다 많이 보내면 상태가 a 상태로 급격하게 변하게 됩니다.

위 표에 있는 Erasable PROM 과 EEPROM 에 대한 차이점을 알아보겠습니다. 다음 사진은 Intel 의 EPROM 입니다. 유리쪽에 UV를 주면 파괴가 되면서 값이 변화합니다.

위 그림에 있는 기계에 집어넣고 20 , 30 분 있으면 해당되는 데이터가 지워지게 됩니다. 여기서 칩을 통째로 집어 넣기 때문에 EPROM은 chip level 입니다. 이러니 불편해져서 EEPROM 이 나오게 된 겁니다.

RAM

- 이름이 잘못 붙여졌습니다. 반도체는 다 Random Access입니다.

- Read /Wirte

- Volatile

- Static or Dynamic

계속 값을 써주어야 하는거 DRAM

값을 홀딩하고 있는 것 SRAM

DRAM의 원리

여기서 트랜지스터는 nMos 입니다. 여기서 nMos는 n-channel MOSFET 인데 그러므로 트랜지스터 윗 부분에 +를 가해줘야 가운데 부분에 n개의 채널이 형성이 됩니다.

gate 에 '+' 를 인가하게 되면 노란부분 (p-type silicon) 쪽이 밀려나면서 저 곳에 ' - '가 차면서 n-channel 이 형성이 됩니다. 형성이 되면 저 초록색 부분 n-type 이 연결이 됩니다.

DRAM은 이런 트랜지스터로 구현이 됩니다.

DRAM 특징

- capacitor 에 한 비트 저장 (전하)

- 쓰지 않아도 이 전하는 누수가 일어나서 사라집니다.

- 즉 계속 refresh 를 시켜줘야합니다.

- 구조가 간단해서 가격이 싸고 속도는 느리기 때문에 Main Memory 에 쓰입니다.

그리고 커퍼시티의 충전과 방전은 곡선 형태로 이루어져있습니다.

DRAM의 동작

- Write : 0 또는 1이면 Capacitor에 충전이 되는 형식으로 Write

- Read : 충전되어 있는 값을 읽음

DRAM의 성능은 물리적인 요소에 의해 결정이 됩니다.

Static RAM

-bi-stable flip-flop (두가지의 상태가 안전적인 플립플롭)

-복잡, 비쌈, 빠름,Cache

C1이 1이라고 봤을때 C2는 0입니다.

그리고 C2가 1이면 C1은 0입니다.

왜이렇게 되는 걸까요? C0이 0이면 연결되어 있는 저 체크된 부분도 0입니다.

저쪽이 0이라면 T4와 T2중에 어떤 게 On이 될까요? T4는 p-mos고 T2는 n-mos 이기 때문에 T4가 On이 됩니다. 마이너스가 인가 되었기 때문에 + 채널이 형성이 됩니다. 그럼 이때 dc voltage는 어떻게 될까요? + 채널이 형성이 되었기 때문에 1이 형성이 됩니다.

이렇게 되면 C2에도 1이라는 값이 됩니다. 그럼 반대편도 1이 넘어갈 겁니다.

그러면 T1, T3 중 뭐가 On이 되나요?

T1이 On이 됩니다. 그러면 Ground 에 들어가게 되는데 이는 0을 의미합니다.

그림이 너무 이상하지만 이렇게 C1에 0이 들어가게 되는거죠. 이렇게 값을 유지가 됩니다. 이렇게 C1은 0, C2는 1인

Bi-stable 한 환경을 유지하게 됩니다.

여기서 Address line에 이 값이 들어오면 어떻게 될까요. T5와 T6가 On이 됩니다. 그러면 왼쪽 Bit line 에는 C1의 값이 0이 들어갈거고 오른쪽 Bit line은 1이 들어가는게 B바 이기 때문에 결과적으로는 0입니다. 그러면 이 SRAM 로직에서 0을 유지하고 있다는 걸 알 수 있습니다.

이게 SRAM입니다. 트랜지스터가 6개인 걸 볼 수 있습니다.

대부분의 SRAM 은 Row Decoder와 Column Circuitry 을 가지고 있습니다. 이를 통해 특정 셀이 선택되고 그 셀을 출력하는 형식입니다.

SRAM vs DRAM

- Both volatile

둘 다 휘발성입니다. 하지만 SRAM 은 전원있으면 피드백을 걸어서 안정적으로 값을 유지하는데 DRAM 은 굉장히 자주 해당 값을 강화시켜주어야합니다.(refresh)

-SRAM은 캐시

-DRAM 은 주기억 장치

ROM(Read Only Memory)

기본적인 입출력이라든지, 명령어라든지 그런 거를 ROM에 구현을 합니다.

-Mask ROM : 제작 단계에서 값이 들어감.

-Programmable(once) : 한번 쓰기면 끝 제작 단계에서 값 넘는게 아님

-Erasble PROM

-Electrically Erasable PROM : EPROM보다 빠르게 지울 수 있는 거

-Flash memory

실제 16메가비트 메모리가 어떻게 이루어져있는지 확인해보도록 하겠습니다.

아래의 데이터 버퍼 쪽을 보면 출력이 4비트라는 것을 알 수 있습니다. (D1,D2,D3,D4로 되어있네요)

또 보면 Refresh Counter가 있네요. 메모리에 refresh 가 필요한 건 DRAM 이라고 이야기를 했습니다.

주소의 길이는 A0~ A10 까지 총 11비트 입니다.

2k 까지 표현이 되는데(k = 10^3, 2^10 = 1024) 이 2k가 Row address 와 Column address 로 분리가 됩니다.

2k가 두개니깐 4M가 됩니다. 근데 출력이 4개가 나오니깐 4 x 4 = 16M 가 나오는겁니다.

Row Address Select : 행을 선택

Column Address Select : 열을 선택

Write Enable : 쓰기 가능

Output Enalbe : 출력 가능, 데이터 버스 쪽으로 가서 공유, 출력이 되는 값이 바로 입력이 되서 refresh합니다. DRAM은 한번 읽으면 지워지기 때문에 Refresh 을 해주어야합니다. DRAM 에 전형적인 구조입니다.

여기서 MUX는 해당값을 읽었으니깐 다시 Refresh 해주는 즉, 다시 써주기 위한 역할을 담당하고 있습니다.

요새는 BGA(Ball-grid array)와 QFP(Quad-flat package) 이 많이 쓰인다고 합니다.

9비트는 512(2^9) 를 의미합니다 . 그러니 디코더가 512 중 한 값을 선택할 수 있는 형태인거죠. 이 디코더가 8개가 있으니 8비트를 뽑아낼 수 있습니다. 근데 이게 행, 열로 두개 이니깐 2^9 X 2^ 9 = 2 ^ 18 = 256K 그리고 한번에 8비트씩(=1bytes) 오니깐 이는 256K byte 를 냅니다.

아래의 모듈은 위에 256K byte 를 내는 모듈을 4개 사용한 겁니다. 그러면 1024 = 1 MByte Module 입니다.

추가로 2비트가 존재해서 Group 을 선택해줍니다.

Error Correction

메모리는 다양한 이유로 오류가 생길 수 있습니다.

이 중에 Soft Error 는 랜덤하게 일어난, 하드웨어가 박살 난게 아니라 고칠 수 있는 형태입니다.

하드웨어가 박살나는건 Hard Failure 라고 합니다. 이런 경우는 고칠 수가 없습니다.

이렇게 Soft Error을 detect 하고 correction 할 수 있는 기법들이 있습니다. 가장 유명한 것이 Hamming error correcting code 입니다.

Hamming code

▶1의 개수가 짝수가 되는 로직을 만들자.

다음과 같이 채워 넣는다면 다음과 같이 됩니다.

근데 이 때 오류가 납니다.

A 에 입장에서 1이 홀수 입니다. B에서는 짝수, C에서는 홀수 입니다. 그러니 A와 C에 포함이 되면서 B에 포함되지 않은 코드에서 에러가 났다라고 결론을 내릴 수 있습니다.

M비트의 오류를 찾기 위해 K비트가 더 필요합니다.

생각해보면 간단한게 12비트에 4비트가 있으면 16비트입니다. 이 16비트(2^4)를 표현하기 위해서는 4비트가 필요합니다. 물론 error가 여러개가 났을때는 말이 좀 달라집니다.

Hamming Code 에 동작 원리에 대해 알아보겠습니다.

다음 표시된 건 Check bits 인데 1이 하나만 있다는 걸 알 수 있습니다. 여기서 다른 수가 이 자리에 1이 있으면 그 걸 다 XOR해줍니다.

이렇게 될겁니다.

예시를 들어보겠습니다.

Input word 가 00111001 이라고 가정해봅시다.

check bits 는 다음과 같이 계산이 됩니다.

그리고 본래 보낼려 하는 데이터에 이 체크 비트 XOR 값이 삼비트만 추가되어 보내집니다. 이때 체크 비트의 자리수에 맞게 추가가 됩니다.

C1 - 0001 - 1

C2 - 0010 - 2

C3 - 0100 - 4

C4 - 1000 - 8

001101001111

여기서 오류가 날 비트는 6번째 비트입니다.

그리고 오류가 다음과 같이 난겁니다.

001101101111

이 값을 다시 체크 비트로 계산해줍니다.

이 값을 원래의 체크비트 값과 XOR 해줍니다.

이러면 0110 = 6 , 6번째 비트에서 오류가 났음을 알 수 있습니다.

이걸 체크비트 값을 Syndrome 이라고 합니다. 이 신드롬 계산 값이 0 이면 오류가 안 난 겁니다.

그럼 두비트가 동시에 에러가 나면 어떡하나요. 다음과 같은 상황이 생깁니다.

원래 로직을 사용하면 더 큰 에러를 발생시키게 됩니다. 그러면 어떻게 해야할까요. '추가비트'를 두면 됩니다. 이 추가 비트 1은 전체 로직을 보면서 짝수가 되게 맞춰줍니다. 그리고 Correction 후 전체를 보고 한번 더 생각했을때 홀수가 되어 버리니깐 ' 아 내가 Correction을 잘 못 했네.' 라는 것을 알 수 있습니다. Correction은 못하지만 Detection은 할 수 있는 형태입니다.

이제 메모리의 종류에 대해 살펴보겠습니다. DRAM을 어떻게 구성하냐에 따라서 또 구분이 될 수가 있습니다.

Synchronous DRAM(SDRAM) 이 있습니다.

-외부 클럭에 의해 동기화되는 DRAM

2Mega 짜리가 8개인 DRAM이 있습니다. 8개라는건 출력 비트가 8bits 라는 겁니다. 주소로 14비트가 들어가고 있는데 이중에 2비트는 4개인 DRAM을 선택하는 용도로 사용이 될 것입니다. 그리고 나머지 12 비트를 가지고 열과 행을 선택하는 거 같습니다. 실제 구성은 정확하게 할 수는 없지만 12비트는 4K 이기 때문에 4개니깐 16M입니다.

DDR SDRAM(Double-data-rate SDRAM)

-Rising 과 Falling 에서 동시에 동작

Cache DRAM

-DRAM 에다가 작은 SRAM을 추가를 한 형태

Flash Memory

굉장히 많이 사용하는 메모리입니다. 요새는 하드디스크도 거의 Flash Memory로 대체가 되었습니다.

이 플래시 메모리의 원리에 대해 알아보겠습니다.

Intel의 NOR 와 Toshiba 의 NAND FLASH가 굉장히 큰 싸움을 벌렸습니다.(1988,1989) (지금은 인텔과 삼성이 플래시 메모리의 절대강자입니다.)

왜 싸웠나면 플래시 메모리를 구성하는 방식에 대해서입니다.

데이터 스토리지 형태(용량) : NAND

읽는 속도는 NOR

쓰는 속도는 NAND

Erase cycle limit : 지속적으로 쓰면 플래시 메모리가 고장이 납니다. 즉 쓸 수 있는 횟수가 제한이 되는 겁니다. 플래시 메모리는 반도체를 파괴시키는 방식으로 사용되기 때문에 쓰면 쓸 수록 고장이 날 수 밖에 없습니다.

그 원리에 대해 알아보겠습니다.

N 채널을 가지고 있는 C MOS 트랜지스터 입니다. P-substrate 이니깐 '+'를 인가해야 작동을 할 겁니다.

근데 플래시 메모리는 이와 좀 다릅니다.

가장 큰 차이점은 Floating Gate 입니다. FG에 전자가 트랙되지 않는 경우 상태가 1입니다.

이 경우는 전자가 FG에 들어있기 때문에 상태가 0입니다.

왜 이렇게 정의가 됐을까요?

a,b에 2.5V의 전압을 인가하면 다음과 같이 채널이 형성이 됩니다.

하지만 c에 2.5 V의 전압을 인가하면 어떻게 될까요?

FG 층에 있는 전자들이 이 전압을 다 잡아먹어버려서 채널이 형성이 되지 않습니다.

더 높은 전압(5V 정도의)을 주면 어떻게 될까요?

이때는 전자가 상쇄도 되고 채널도 형성되게 됩니다.

이 그래프는 상태가 1, 0 이냐에 따라서 채널을 형성하기 위한 전압의 크기를 표현한 것 입니다.

그럼 NOR 타입과 NAND 타입의 차이는 무엇일까요?

보면 Ground Select Transistor 가 있고 Bit line 이 있습니다. 만약 그라운드가 ON이 될려면 모든 Word line 이 1이 나온다면 Bit line은 0이 됩니다.

반면에 NOR는 하나만 1이 나와도 0이 됩니다.

그럼 예시로 NAND flash data 를 읽어보겠습니다.

만약 word line 4를 읽고 싶다면 어떻게 해야할까요?

딴값을 모두 아주 높은 전압을 줘서 ON을 시켜야합니다. 만약 낮은 전압을 걸면 상태 0인 경우에는 ON을 시킬 수가 없기 때문입니다. 이 상태에서 Word Line 4 에 2.5 전압을 가해서 ON이 되면 상태 1이구나, 더 높은 전압을 가해야하면 상태 0 이구나를 알 수 있습니다. 이렇게 골치 아프기 때문에 읽을 때 속도가 좀 느린 것 입니다.

플래시 메모리가 더 무서운 이유는 따로 있습니다.

트랜지스터에는 0 ,1 두개의 정보량이 저장이 됩니다. 하지만 트랜지스터는 level을 둘 수 가 있습니다. 0 ,1 이 아님 더 많은 비트의 정보량을 저장할 수가 있는 것입니다. (화학 물질로 트랜지스터를 어떻게 구성하느냐에 따라서) 요새는 셀마다 3비트는 기본으로 저장할 수 있다고 합니다.

이렇게 오늘은 내부 메모리(SRAM, DRAM, Flash Memory)에 대해 배워 보았습니다. 수고하셨습니다.

'공부 > 컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터구조7 Input/Output (0) | 2020.06.22 |

|---|---|

| 컴퓨터구조6 External Memory (0) | 2020.06.13 |

| 컴퓨터구조4 Cache Memory (0) | 2020.06.05 |

| 컴퓨터구조3 CPU (0) | 2020.05.29 |

| 컴퓨터구조2 Process (0) | 2020.05.27 |